笔试相关

笔试相关

公司1

1.数字芯片设计工程师 2025届硬件提前批

1.岗位要求

职位描述

1.负责IP级.SoC级架构设计和RTL实现工作;

2.优化模块和系统PPA;

PPA是数字IC设计逃不开的概念,分别是P(Performance)、P(Power)和A(Area),分别代表芯片的性能、功耗和面积。

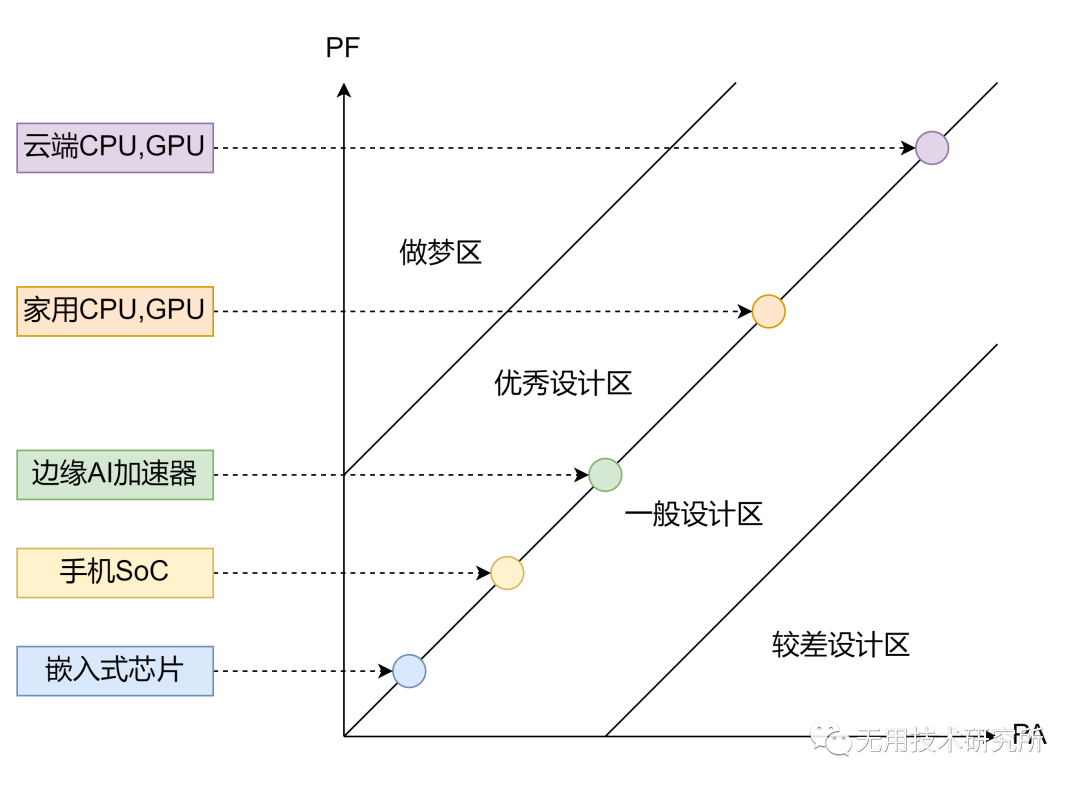

- PF:即性能(Performance)和功能(Function),这里将原始的Performance拆分为两个部分。功能(Function)是定性的,即这块芯片支持什么功能,性能(Performance)是定量的,表示这块芯片这个功能支持的怎么样,这两个指标用来衡量芯片的能力。

- PA:即功耗(Power)和面积(Area),这里使用的就是原始的P和A概念,这两个指标用来衡量芯片的消耗。

3.配合芯片验证工作,满足准出要求;

4.参与芯片综合,并配合芯片后端实现工作;

5.配合FPGA测试.系统联调.芯片板级测试等工作。

职位要求

1.微电子/通信/计算机/自动化等相关专业,硕士及以上学历;

2.精通Verilog/VHDL设计语言;

3.有实际FPGA/ASIC经验优先,有脚本能力者优先;

- TCL:相关链接

- 在Linux操作系统下的VCS(用来跑 Verilog 仿真的软件),都是通过命令来控制的,当然可以一行一行的敲命令来运行,但是为了复用性和易于维护,把所有的命令都写在一个文件里面,这个充满命令的文件被叫做脚本,通过运行这个脚本里面的一大堆命令来启动和运行VCS。写脚本的语言就是脚本语言,这也就是脚本语言为什么必要了。因为不会写脚本,软件有可能都没办法运行。

4.有相关综合,DFT及STA时序分析经验者优先;

DFT https://blog.csdn.net/m0_52840978/article/details/123242313

DFT是design for test(可测性设计)的缩写,就是在芯片设计过程中,加入可测性逻辑。有的公司把该职位归到前端设计,有的归到中端实现。

DFT主要是通过在芯片中加入可测性逻辑,等芯片制造出来,在ATE(Automatic Test Equipment,自动测试仪)设备上通过可测性逻辑对芯片进行测试,挑出有制造缺陷的芯片并淘汰掉,留下没有制造缺陷的好芯片。

5.良好的团队合作意识和沟通能力。

2.笔试相关内容

在多周期设置中,Setup的周期是X,设置Hold周期为X-1

当clock的周期是10ns,对于模块的input需要添加input delay,假设外部延迟是6ns,内部延迟是4ns,那模块的input delay需要设置为 6ns

MOORE/MEALY状态机-相关链接

- 摩尔型状态机,又称为Moore机器,其特点是输出仅与当前状态有关,而与输入信号无关。这意味着,无论输入如何变化,只要状态不发生改变,输出就保持不变。

- 米利型状态机,或称为Mealy机器,其输出不仅取决于当前状态,还取决于当前的输入信号。因此,即使状态没有变化,只要输入信号改变,输出也可能随之改变。

https://www.nowcoder.com/feed/main/detail/a0ed313160cd4d36bbd0dfe9ca81936b

数电 模电 强电大杂烩

- https://www.nowcoder.com/feed/main/detail/dc616fa682f549dda41b2e75883b49a2

电子研发类笔试 题型:选择题30个

考试内容:数电,数字逻辑电路设计,PCB 设计,模电几乎没有。

https://www.nowcoder.com/feed/main/detail/5971112030694e0a8c68000d82480226

小米提前批的硬件咋还考模集啊!一共三十道题,全是选择题,数字电路的部分都还好,模拟部分是真的没想到啊,居然考模集,模电的只涉及到了LDO,放大器部分全是拉扎维书上的东西,全忘了啊

3.岗位工作内容:数字IC

前端设计

RTL IP设计:从算法协议到RTL coding的能力;

SoC设计集成/验证:总线、功耗、系统架构的能力;

SOC侧重将IP,模块集成形成一个系统,所以片上互联总线和外设接口是掌握的重点。片内互联总线一般是AMBA总线。外设接口又分为低速接口和高速接口,其中低速接口包括I2C,UART,SPI等,高速接口包括SATA,USB,PCIE,DDR等;

验证

FPGA原型验证:HAPS -> HAPS®-100原型系统、芯片验证技术 |HAPS与高性能ASIC原型验证

UVM验证:SV、UVM主流验证方法学 ->UVM芯片验证

EMU验证:zebu、帕拉丁 -> 芯片验证应用|基于ZeBu平台的虚拟主机应用方案

综合

逻辑综合就是将HDL代码翻译成门级网表netlist;

STA

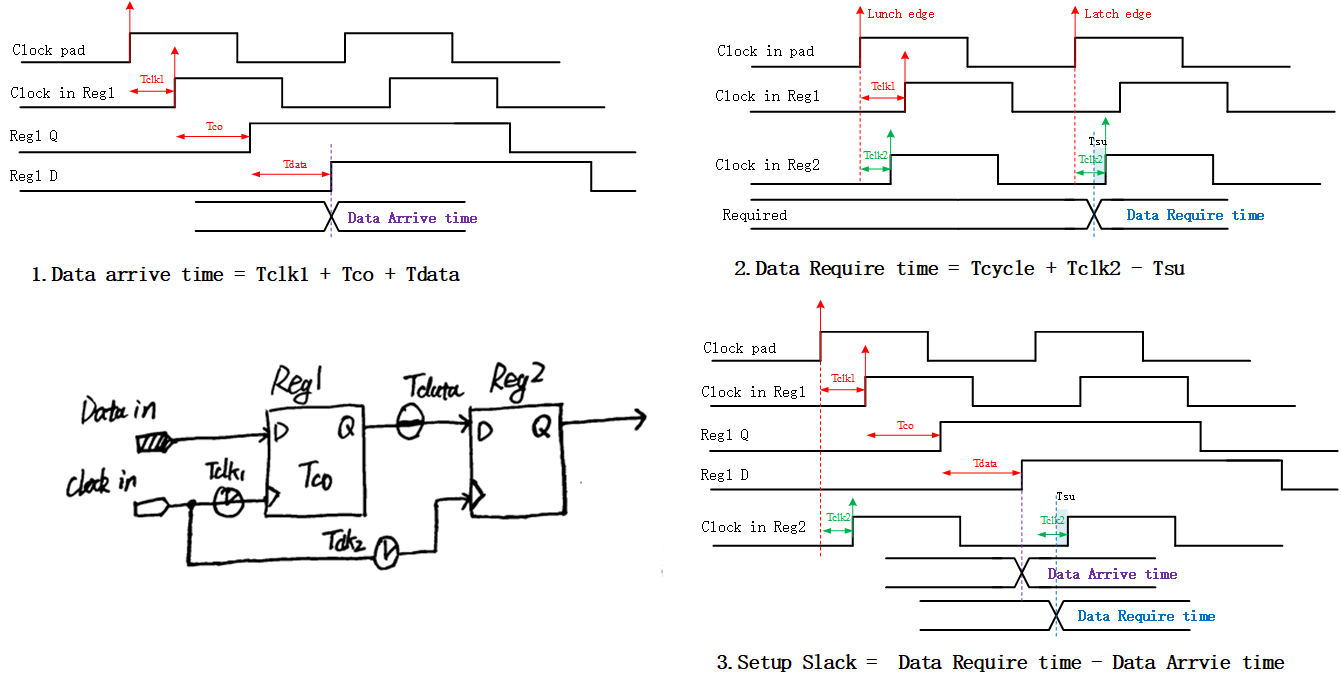

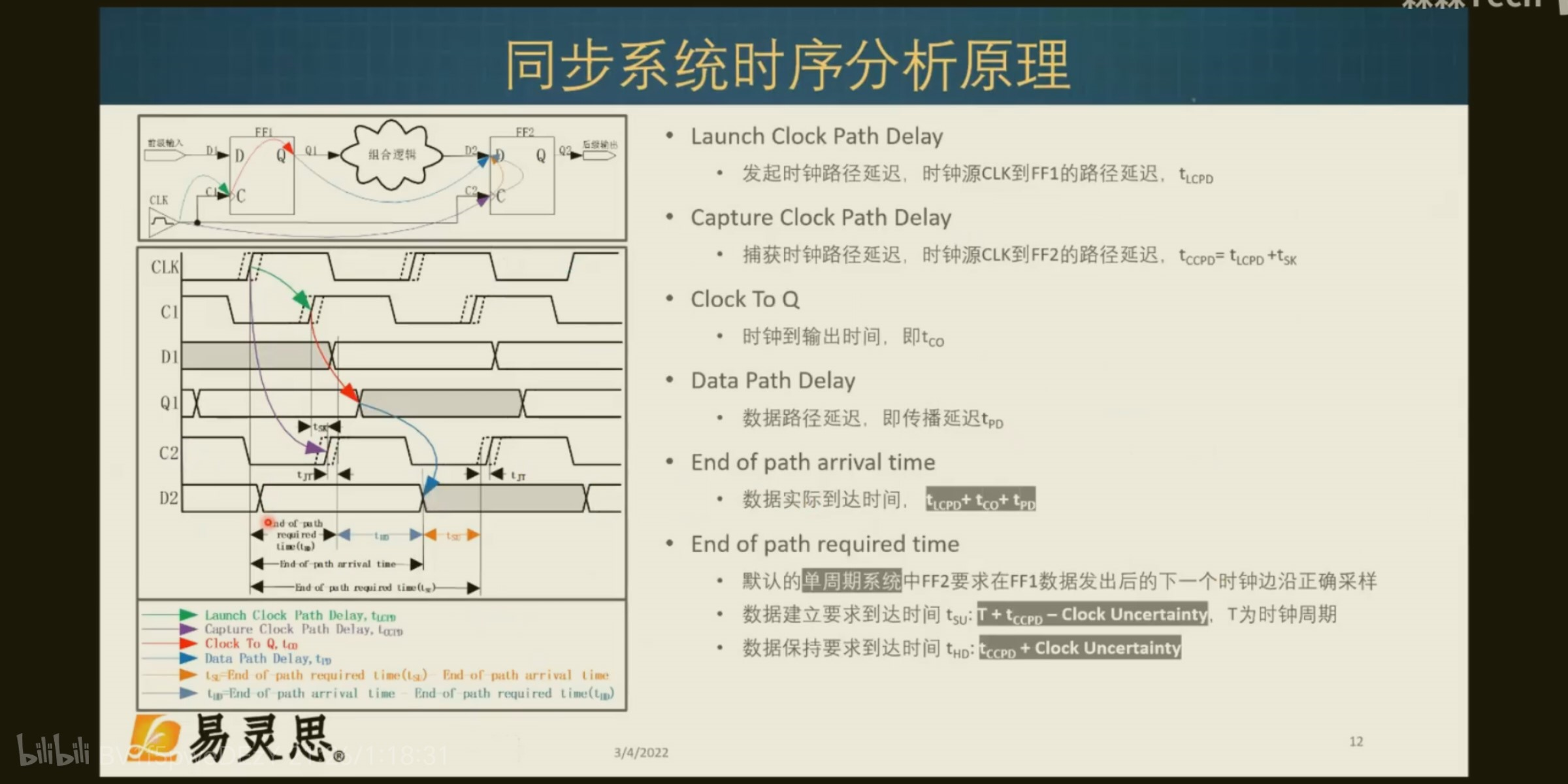

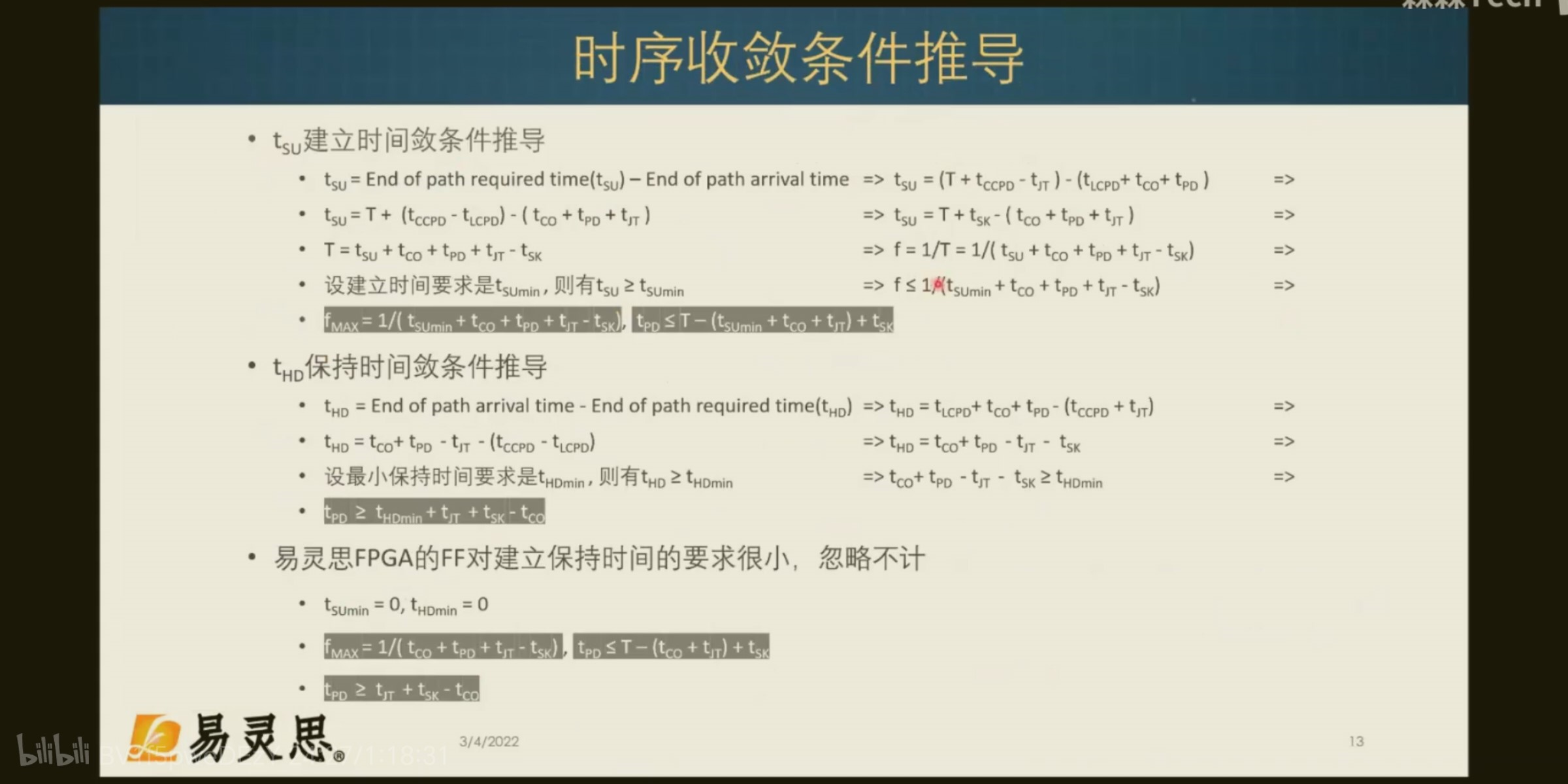

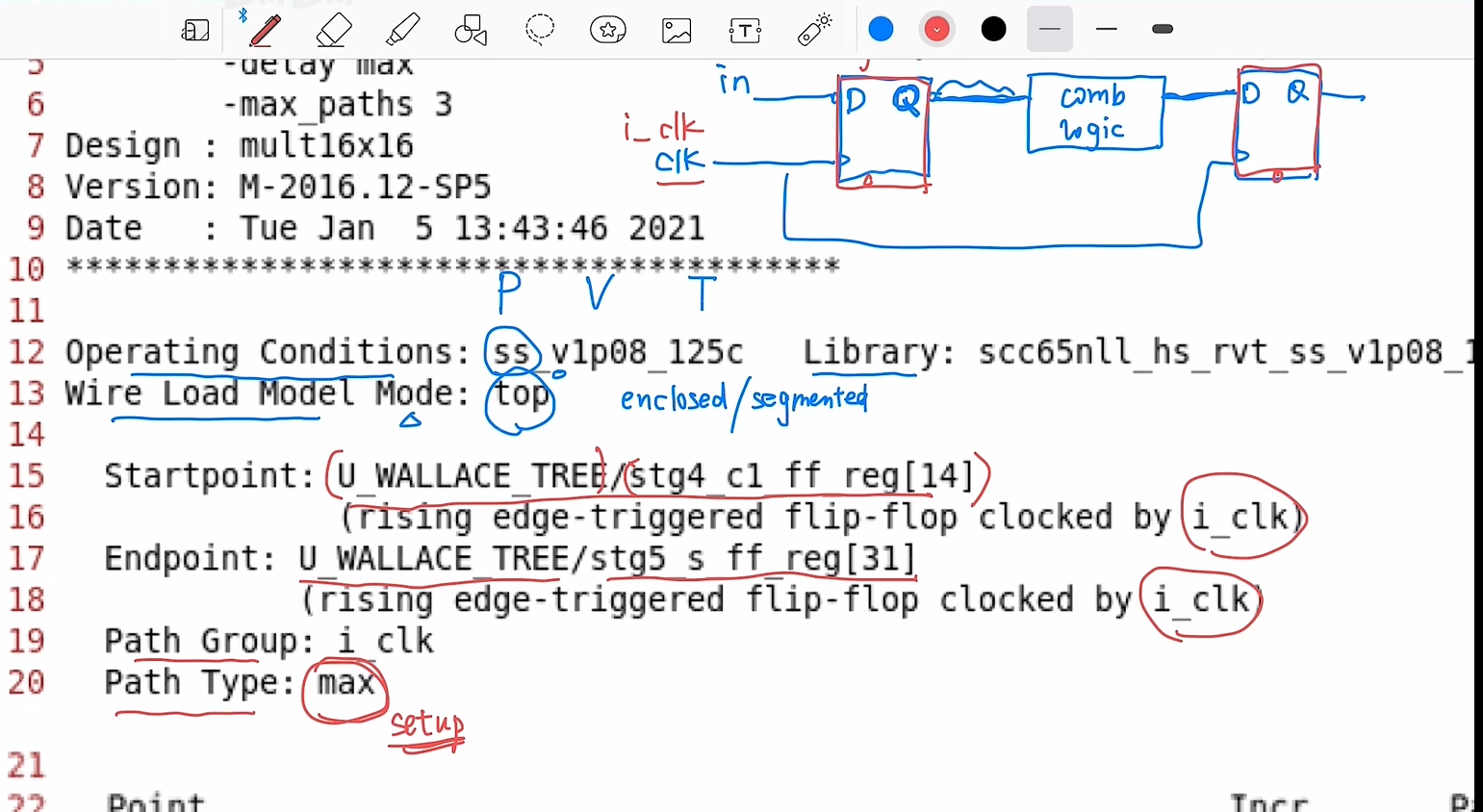

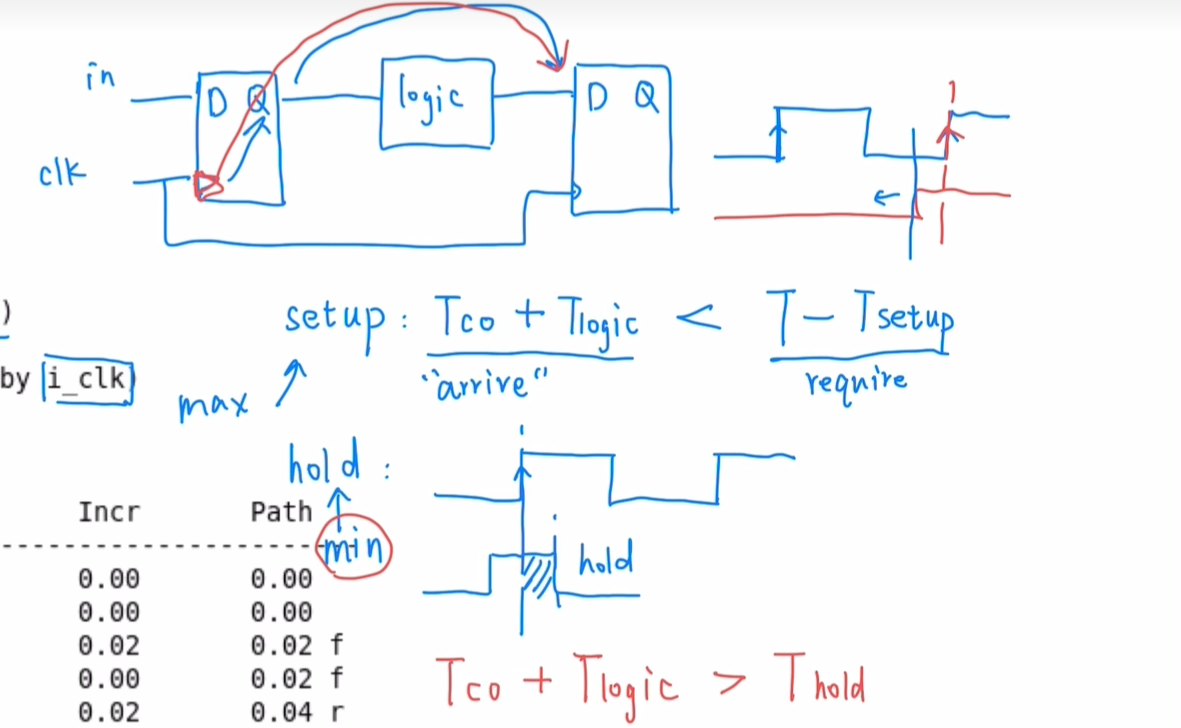

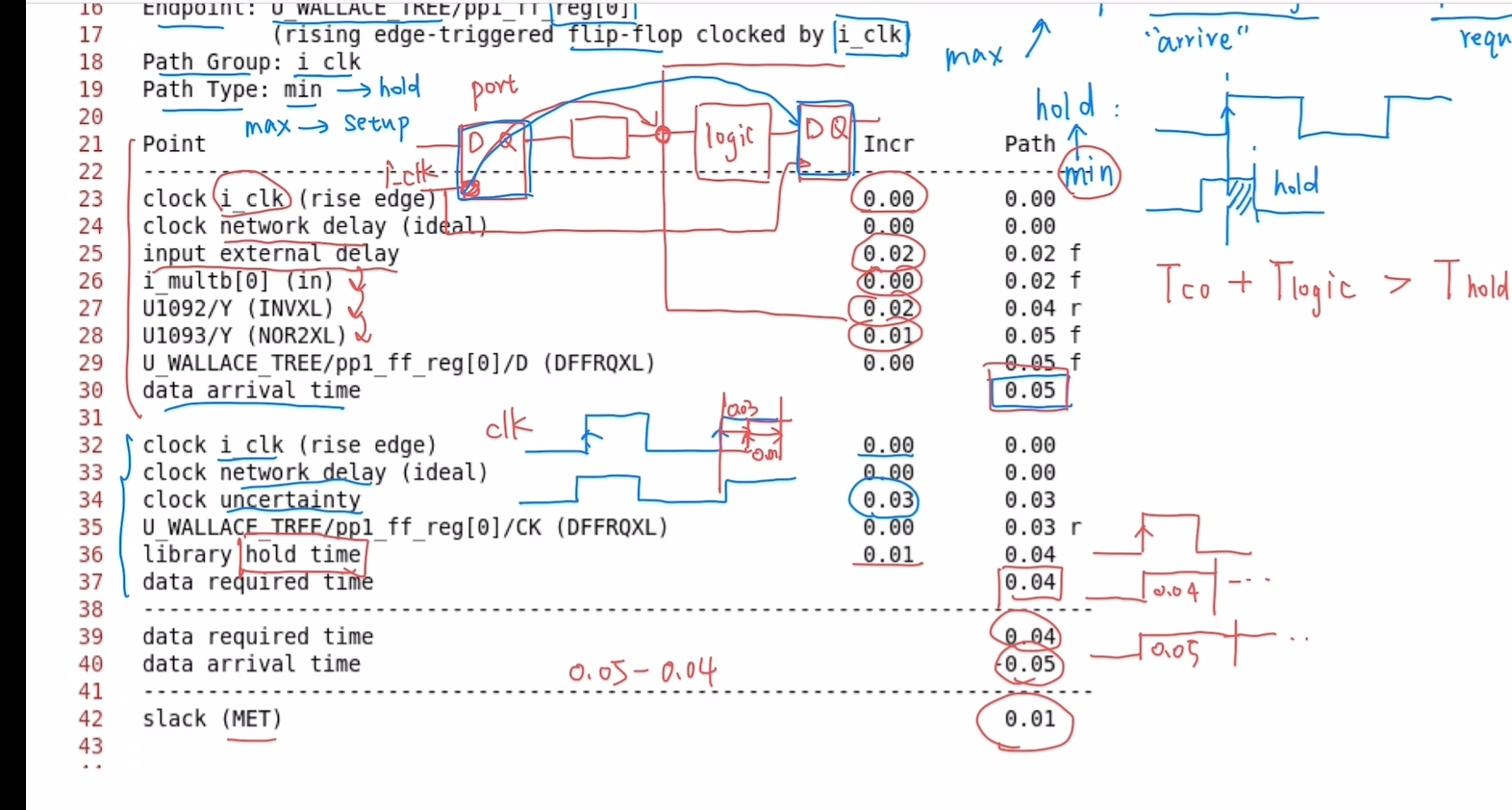

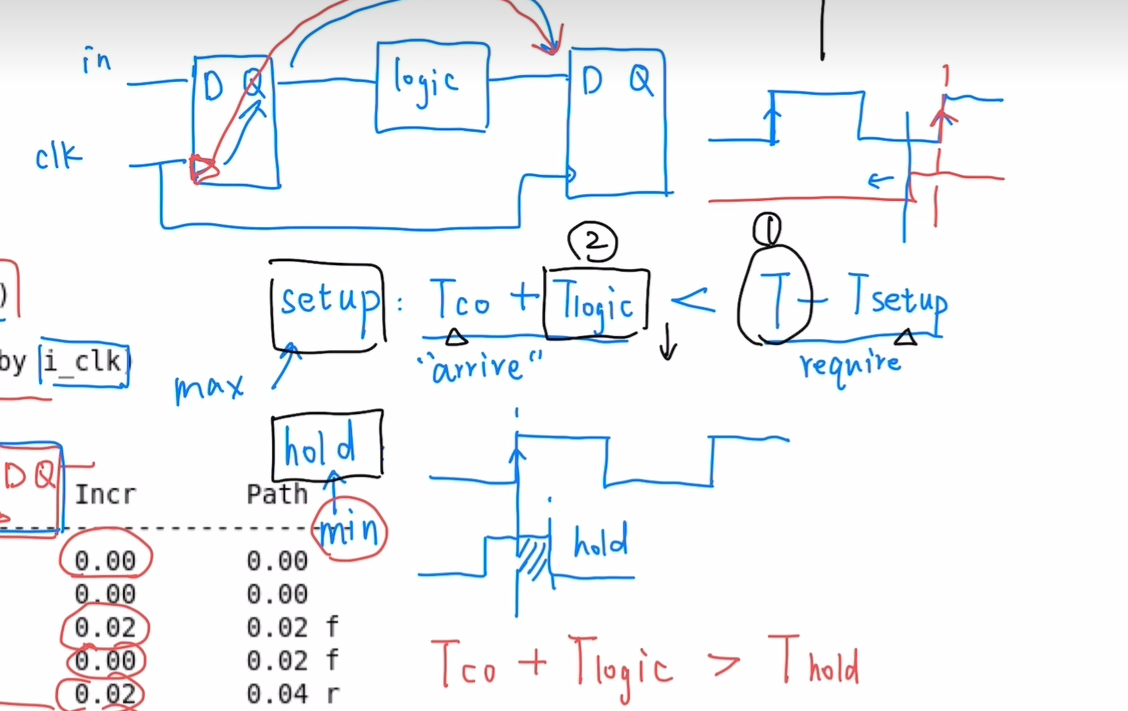

Static Timing Analysis(STA),静态时序分析,它主要是在时序上对电路进行验证,检查电路是否存在建立时间(setup time)和保持时间(hold time)的违例(violation),一个寄存器出现这两个时序违例时,是没有办法正确采样数据和输出数据的,所以以寄存器为基础的数字芯片功能肯定会出现问题。

DFT

Design For Test,可测性设计。芯片内部往往都自带测试电路,DFT的目的就是在设计的时候就考虑将来的测试。DFT的常见方法就是,在设计中插入扫描链,将非扫描单元(如寄存器)变为扫描单元;如bist、Scan Design、JTAG、ATPG等;

后端

物理验证、布线布局、静态时序分析、等价性检查、功耗分析

2.笔试题-回忆

问的非常基础,电路,模电,数电,以及System Verilog,重点在之后的面试。暴露了基础不牢的缺陷。 ---24.07.23

1.加法器和寄存器

加法器属于组合逻辑电路的一种,这是因为它们执行的是固定的逻辑操作,根据输入直接产生输出,而不需要记忆或存储任何状态。组合逻辑电路的分析和设计主要涉及分析逻辑图、列出真值表、写出逻辑表达式、逻辑函数化简以及分析电路的逻辑功能。

寄存器的设计和实现依赖于时序逻辑电路的工作原理,即其输出状态不仅依赖于当前的输入,还依赖于过去的输入和时钟信号的变化。时钟信号在寄存器中扮演着关键角色,它控制数据的输入和输出,确保在时钟上升沿或下降沿时,数据能够稳定地从输入复制到输出。这种同步的数据传输方式使得寄存器能够在时序逻辑电路中起到存储和同步的作用。

2.关于SYSTEM VERILOG 和 VERILOG的区别

https://blog.csdn.net/qq_46264636/article/details/135548541

3.门电路

https://zhidao.baidu.com/question/335283788.html

由于Vcc为5V,当A、B任一端为0V时,由于D1或D2,或两者都处于导通状态,基于其导通压降只有0.7V,所以Y点电压都将被钳位于0.7V;

当A、B两端同时处于3伏时,虽然两二极管还是一样处于正向导通状态,但此时对A端来说,Y点电压为A点电压加二极管正向压降0.7V,即3.7V,同样对B端来说Y点电压也应为3.7V,这样,在A、B两端同处3V电压时,Y点电压将保持于3.7V。

构成一个两输入端的正逻辑与门电路

4.门电路存在延迟时间是组合逻辑电路产生竞争冒险现象的根本原因。

5.以下哪个触发器存在竞态现象?

关于各类触发器:https://blog.csdn.net/weixin_46817835/article/details/124140309

对于D触发器:https://blog.csdn.net/GOGOmusic/article/details/79449376

空翻现象,又称为竞态现象,是数字电路中的一个术语,指在同一个时钟脉冲信号作用区间内,由于时钟脉冲的宽度过大,触发器出现在“0” “1” 两逻辑中多次翻转的现象。它限制了同步RS触发器在实际工作中的正常应用。

6.对于多级放大电路

7.关于SystemVerilog Checker的说法中,错误的是

https://blog.csdn.net/qq_39794062/article/details/113376274

8.对于一阶电路及其响应

9.对于一个电路图,其含有逻辑门,也含有寄存器,因为含有寄存器,所以是时序逻辑电路,由因为存在时钟信号,同时也是mealy型时序逻辑电路,这样对吗?

如果电路图中除了包含寄存器外,还存在时钟信号,并且输出直接依赖于当前的输入信号(除了内部状态),那么它确实可以被视为Mealy型时序逻辑电路。时钟信号在时序逻辑电路中扮演着重要的角色,它用于控制寄存器的状态更新,并协调电路中的操作顺序。

10.关于RCL串联谐振电路

11.电路中两个互感线圈,串并联等效?

11.D触发器可以作为存储型的时序电路吗?

12.某三极管电路,小信号放大增益为?

3.(24.08.02)SOC设计工程师-面试

1. 岗位要求

职位描述

1.参与SOC系统设计.分析和开发工作;

2.参与SOC顶层或子模块的设计工作,根据需求制定各模块的设计规格和详细设计方案;

3.完成RTL代码以及质量检查(lint,CDC,预综合等)预综合并输出timingspec;

4.结合产品实际需求,在chiplet片间互联.处理器微架构等前沿技术领域进行探索和分析;

5.跟踪和研究各个领域的技术进展及业界新技术。

职位要求

1.微电子或者计算机专业,硕士及以上学历;

2.掌握Verilog语言并具备一定的coding能力;

3.一定程度上掌握SOC的设计流程,并熟悉Synopsys/Cadence/Mentor等公司的EDA工具优先;

4.熟悉计算机体系结构,对主流处理器系统微架构演进和体系结构优劣势等都有深入理解者优先;

5.熟悉大型复杂SOC系统架构.总线设计.DDR控制和调度策略.片间互联技术并有相关研发项目经验者优先。

2.相关面经

https://www.nowcoder.com/feed/main/detail/90343a13169b4bbe85952ce3786fcd23

3. 涉及知识

3.1 SoC设计流程

- 理解SoC的基本概念,包括其组成部分(CPU、GPU、DSP、内存控制器、外设等)和功能。

- 熟悉不同类型的SoC设计,如面向移动设备、嵌入式应用或高性能计算的SoC。

- SoC设计更需要了解整个系统的应用,定义出合理的芯片架构,使得软硬件配合达到系统最佳工作状态,如总线的设计使得总线传输吞吐量满足操作处理的需求,与外部存储器的接口正确等。因而,软硬件协同设计被越来越多地采用。

- SoC 设计是以IP 复用为基础的。因而,基于IP 模块的大规模集成电路设计是硬件实现的关键。

4. 面试与总结

笔试分数:71,SystemVerilog部分不会(简单了解即可)

1.和低功耗SoC面试官讨论问题,(大概20分钟)

其指出 针对SOC设计,重点关注:

- 异步处理

- 低功耗设计(这个一般跟项目走,外部资料少)

- AXI等协议要搞懂,问了我是否了解,我说就是简单了解

2.询问问题

2.1 SoC设计工程师具体在干些什么?

---先是基础的”连连看“工程师,先是使用第三方的IP核,最后是要统筹。

2.2 对于熟悉计算机体系架构?

需要熟悉ARM架构,其实现软件做的事情,硬件来做,如果有这个概念的理解,更好

3.本来不用写题,我自己提出要看看,暴露了自己verilog编码的不熟练

5. 主动手撕的结果

题目:异步信号处理,单bit信号从慢时钟域到快时钟域,从慢时钟域到快时钟域。

公司2

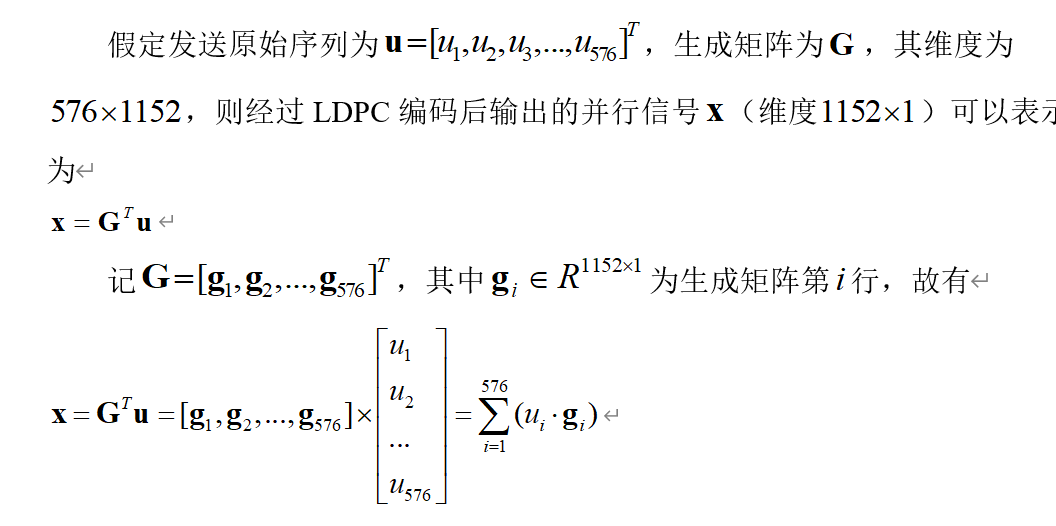

1. LDPC编译码矩阵计算

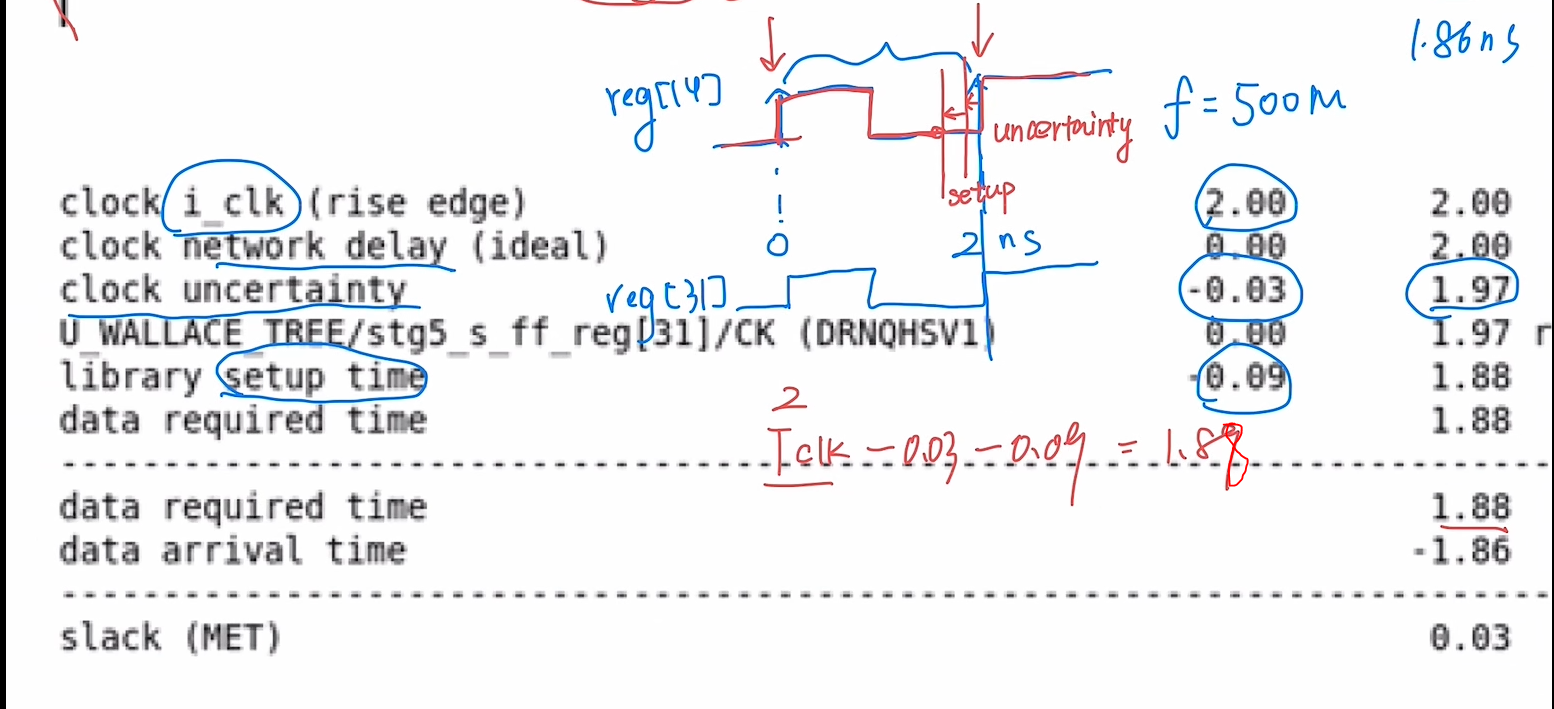

2.建立时间裕量

Tcycle+Tclk2-Tclk1-Tco-Tdata>Tsu

若 Tclk2=Tclk1,{Tsu}min=0

即Tcycle-Tco-Tdata>0

公司3

1.SLICEM、SLICEL的区别?

https://docs.amd.com/v/u/en-US/ug474_7Series_CLB

Every slice contains:

• Four logic-function generators (or look-up tables)

• Eight storage elements

• Wide-function multiplexers

• Carry logic

These elements are used by all slices to provide logic, arithmetic, and ROM functions.

In addition, some slices support two additional functions: storing data using distributed RAM and shifting data with 32-bit registers. Slices that support these additional functions are called SLICEM; others are called SLICEL.

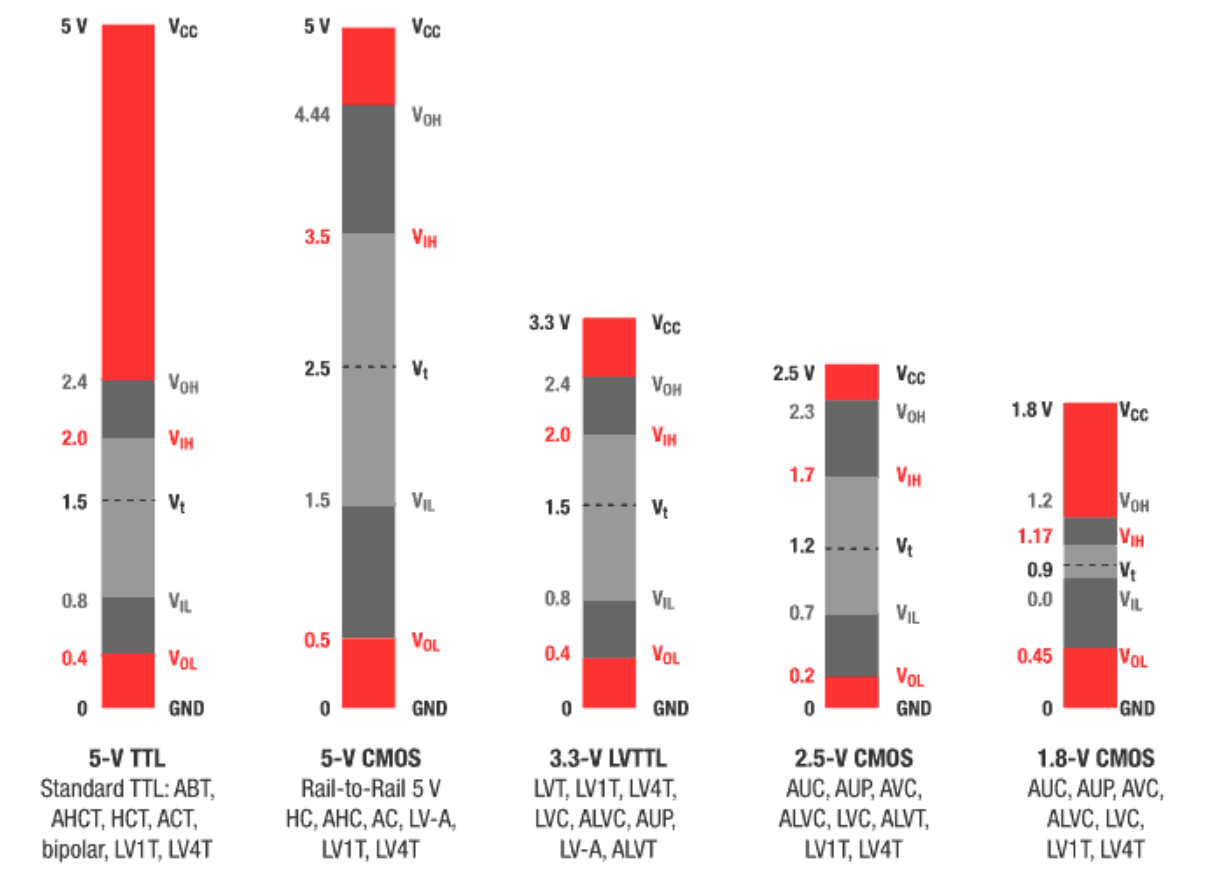

2. 3.3V LVTTL的电压排序

https://e2echina.ti.com/support/machine-translation/mt-logic/f/mt-logic-forum/598687/sn74lvc1t45-ttl-5v-lvttl-3-3v

3. 总线信号的同步,可打两拍吗?

https://blog.csdn.net/qq_38374491/article/details/119079054

什么多比特不能采用打两拍的方法进行跨时钟域同步?

原因1:假设从时域A垮到时域B,是域A从00变到11,在时域B还能采样到从00变到11吗?在时域B中,时钟的上升沿来的时间是肯定一致的,但是各个bit从时域A到达时域B的时间是不一样的,slack不一样,亚稳态恢复到稳态的时间也是不一样的。因此也就是说00中的两个0并不是同时变成1的,因此子时域B中可能采到中间态01或10。 原因2:还有一个原因是单比特发送亚稳态的概率变成多bit后概率会大很多。我们不这样做是可以降低亚稳态发生的概率的。

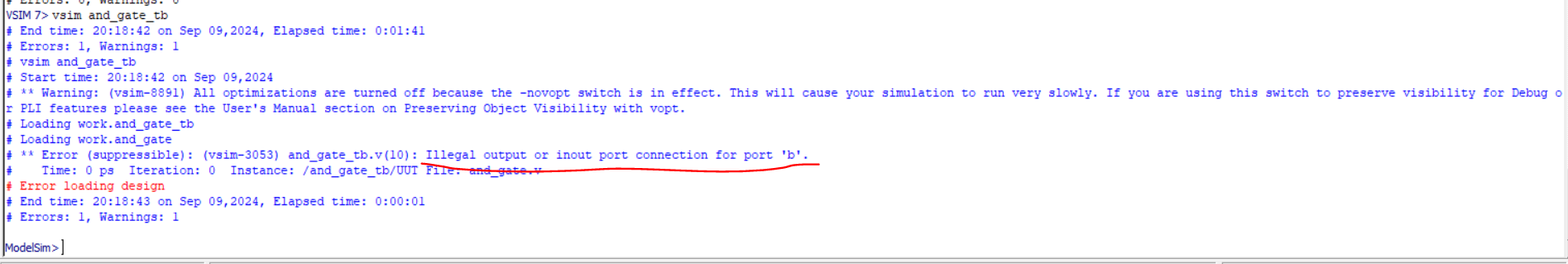

4. 端口类型input定义为ouput,modelsim的仿真会显示什么?

module and_gate (

input wire a,

output wire b,

output wire y

);

assign y = a & b; // 与门逻辑

endmodule

Illegal output or inout port connection for port 'b'.5.serdes的均衡如何实现,是在发端吗?

SERDES(序列化/反序列化)均衡通常是在接收端实现的,但也可以在发端进行一定的均衡处理,以改善信号的完整性。

1. 发端均衡 在发端,均衡可以通过以下方式实现:

- 预加重(Pre-emphasis):在发送信号前,增强某些信号的电平,尤其是高频成分,以抵消信道中的高频衰减。这有助于提高接收端对信号的理解。

- 抖动减少:通过调整发送波形来减少信号中可能存在的抖动,从而提高信号的稳定性和可靠性。

2.接收端均衡 接收端的均衡是更常见的实现方式,主要包括:

适应性均衡(Adaptive Equalization):接收端使用算法动态调整均衡参数,以适应变化的信道条件。这可以通过使用均衡器(如FIR滤波器)来实现,旨在补偿信道引起的失真和衰减。

定制滤波器:根据信道特性使用特定的滤波器来恢复原始信号。这种滤波器的设计通常需要对信号路径的传输特性有深入理解。

6. BUFG,BUGH,BUGR,BUFIO,这里哪些属于时钟网络?

- BUFG(Global Buffer for Clocks):这个是时钟缓冲器,用于分布全局时钟信号。它能够将时钟信号从一个源分配到多个目的地,保持时钟信号的质量和稳定性。

- BUFGH(Global High-speed Buffer for Clocks):这是一个高速度的全局时钟缓冲器,专门设计用于支持高速时钟信号的分配。

- BUFGT(Global Buffer for Differential Clocks):这是一个差分时钟缓冲器,用于处理差分时钟信号,确保信号的对称性和可靠性。

- BUFIO(Input/output Buffer for Clocks):这是时钟输入/输出缓冲器,用于处理I/O端口上的时钟信号。它可以帮助将外部时钟信号引入内部信号处理。

7. 常见的时序优化方法,下面的各项对吗?

优化算法和代码,降低资源使用率算法

这个说法有一定道理,优化算法可以提高整体性能,但特别强调“资源使用率”可能并不是直接影响时序的因素。时序优化更关注建立时间和保持时间的满足,尤其是在时钟频率较高的情况下

使用流水线

具有布局布线以实,对于链接两个模块的信号增加流水线

RAM一般REG型输出,约束RAM的物理位置

这个说法有些模糊。虽然使用寄存器输出数据(而不是直接接RAM的输出信号)可以帮助提高时序性能,并且合理约束RAM的位置可以改善布线延迟,但仅仅说“RAM一般REG型输出”可能会让人误解。具体应该根据设计架构和FPGA特性来处理。

FPGA中的RAM输出一般是REG型吗?

在FPGA设计中,RAM的输出并不总是以寄存器(REG)型的方式输出,但通常会采用某种形式的寄存器化来提高时序性能。以下是一些相关的要点:

- 寄存器化输出:为了减少组合逻辑的延迟和提高时序有效性,很多设计会将RAM的输出连接到寄存器。这意味着即使RAM的原始输出是组合作为信号,它们也会被寄存器包裹,从而形成时序路径的延迟。

- 时序优化:在高频率的设计中,直接连接RAM输出到其他组合逻辑可能会导致时序违例,因此通常会建议在RAM的输出之后增加寄存器,以确保满足建立时间和保持时间的要求。

- FPGA特性:FPGA的具体实现可以影响RAM输出的行为。在一些FPGA中,RAM块自身可能已经内置了寄存器化机制,比如在写入时能够选择是否添加读取时的寄存器。

8.FPGA内部的锁相环或时钟管理单元,主要有哪些功能?

FPGA内部的锁相环(PLL)和时钟管理单元(Clock Management Unit, CMU)通常具备多种功能,主要包括以下几项:

- 时钟频率生成:PLL可以产生多种频率的时钟信号,从输入时钟信号生成不同频率的输出时钟,以满足设计需求。

- 时钟相位调整:PLL允许用户调整输出时钟信号的相位,以实现时序对齐,改善系统性能。

- 时钟树分配:CMU可以对时钟信号进行分配和路由,将生成的时钟信号分配到内部不同的模块或逻辑单元。

- 时钟倍频和分频:通过调整PLL的反馈和分频比,可以实现时钟信号的倍频或分频。

- 抖动控制:PLL和CMU通常具有滤波器,有助于减少时钟信号中的抖动,以提高时钟质量和系统可靠性。

- 时钟启用和禁用:时钟管理单元可以实现对时钟信号的启用和禁用,从而降低功耗和管理系统状态。

- 输入时钟监测:一些FPGA中,PLL和时钟管理单元能够监测输入时钟的状态,确保系统在异常情况下能够自动调整。

- 动态频率变化:某些FPGA支持动态改变时钟频率,适应不同的工作负载需求,提高系统的灵活性。

9.FPGA的PLL功能有相移和频率合成?抖动滤波属于吗?

抖动滤波:抖动滤波虽然不是PLL的主要功能,但它确实是PLL设计中的一个重要部分。PLL内部通常会有滤波器,用于抑制输入时钟信号中的高频噪声和抖动。因此,抖动滤波可以被视为PLL实现稳定和高质量时钟信号的重要手段。

10. BRAM资源可以用作构建FIFO吗?

可以

11. FPGA中的约束包括:对管脚,区域,时序以及后仿约束?

- 管脚约束(Pin Constraints):定义信号与FPGA引脚之间的映射关系,包括输入、输出、和双向引脚的配置。

- 区域约束(Placement Constraints):指定设计中某些逻辑块或模块的放置区域,以优化性能和降低延迟。

- 时序约束(Timing Constraints):确保信号在特定时间内稳定,例如设定时钟频率、输入输出延迟等,以满足系统性能要求。

- 后仿约束(Post-Layout Constraints):用于在布局后进行验证,帮助确保设计在实际硬件中表现符合预期。

后仿约束:

后仿约束(Post-Layout Constraints)是FPGA设计流程中的一个重要环节,主要用于验证设计在实际布局后(布线完成后)的时序和功能性。这些约束有助于确保ASIC或FPGA内部的信号能够在实际工作环境中可靠地传播,并满足设计要求。以下是一些关键点:

1.定义与目的

后仿约束用于在布局布线完成后对设计进行时序分析,确保各个信号在预定时间内到达目标位置,以避免潜在的故障和不稳定性。

- 常见的后仿约束

- 输入和输出延迟:定义输入信号进入FPGA的时间窗口,以及输出信号从FPGA释放的时间窗口。

- 时钟约束:指定时钟信号的频率、相位和偏移,用于确保时钟信号的稳定性。

- 多周期路径约束:对于一些特殊情况,定义一些信号在多个时钟周期内传播,而不是在单个时钟周期内完成。

- 异步路径约束:用于定义异步信号之间的时序要求,确保在不依赖时钟边缘的情况下,信号仍能可靠传播。

- 工具与流程

后仿约束通常与EDA工具一起使用,这些工具能够进行时序分析和后仿,确保设计符合时序规范。常见的软件工具包括Xilinx Vivado、Intel Quartus等。

- 验证和调试

- 时序分析:使用后仿约束,可以进行静态时序分析,检测潜在的时序违例。

- 波形仿真:通过仿真软件检查设计的功能性,确保在实际布局和布线后的行为符合预期。

5. 优化

若在后仿中发现时序违例,可以根据分析结果进行优化,比如重新布线、调整时钟策略或改变设计逻辑。

总之,后仿约束在FPGA设计中至关重要,确保设计在实际硬件中能够稳定可靠地运行

2.判断

时序仿真不涉及具体的硬件特性,如延时特性。

- 判断:错

- 理由: 时序仿真是为了确保电路在给定时钟周期下正确工作,涉及具体硬件特性,包括延时特性,以便分析信号在时间上的关系。

建立保持时间都是为了稳定采样

- 判断:对

- 理由: 建立时间(Setup Time)确保数据在采样前稳定,保持时间(Hold Time)确保数据在采样时后仍然稳定,二者都是为了避免在采样时出现不正确的数据。

FPGA的管脚输入为单端时,不可以使用全局输入时钟输入管脚的N端

- 判断:对

- 理由: 在单端输入配置下,通常只使用时钟输入的P端(正端),N端(负端)会被视为悬空,不应该用作输入。

IIC的SDA对外输出仅有0或高阻,不存在其他情况

- 判断:对

- 理由: IIC协议中,SDA线在数据传输中只有低电平(0)和高阻抗状态,高电平(1)是由上拉电阻实现的,外部设备在SDA上只能驱动低电平或者置为高阻态

Verilog的每一行都是以“;"结束的

判断:错

理由: 虽然大部分语句需要以分号结尾,但模块、任务和函数定义等结构并不需要在最后一行加分号

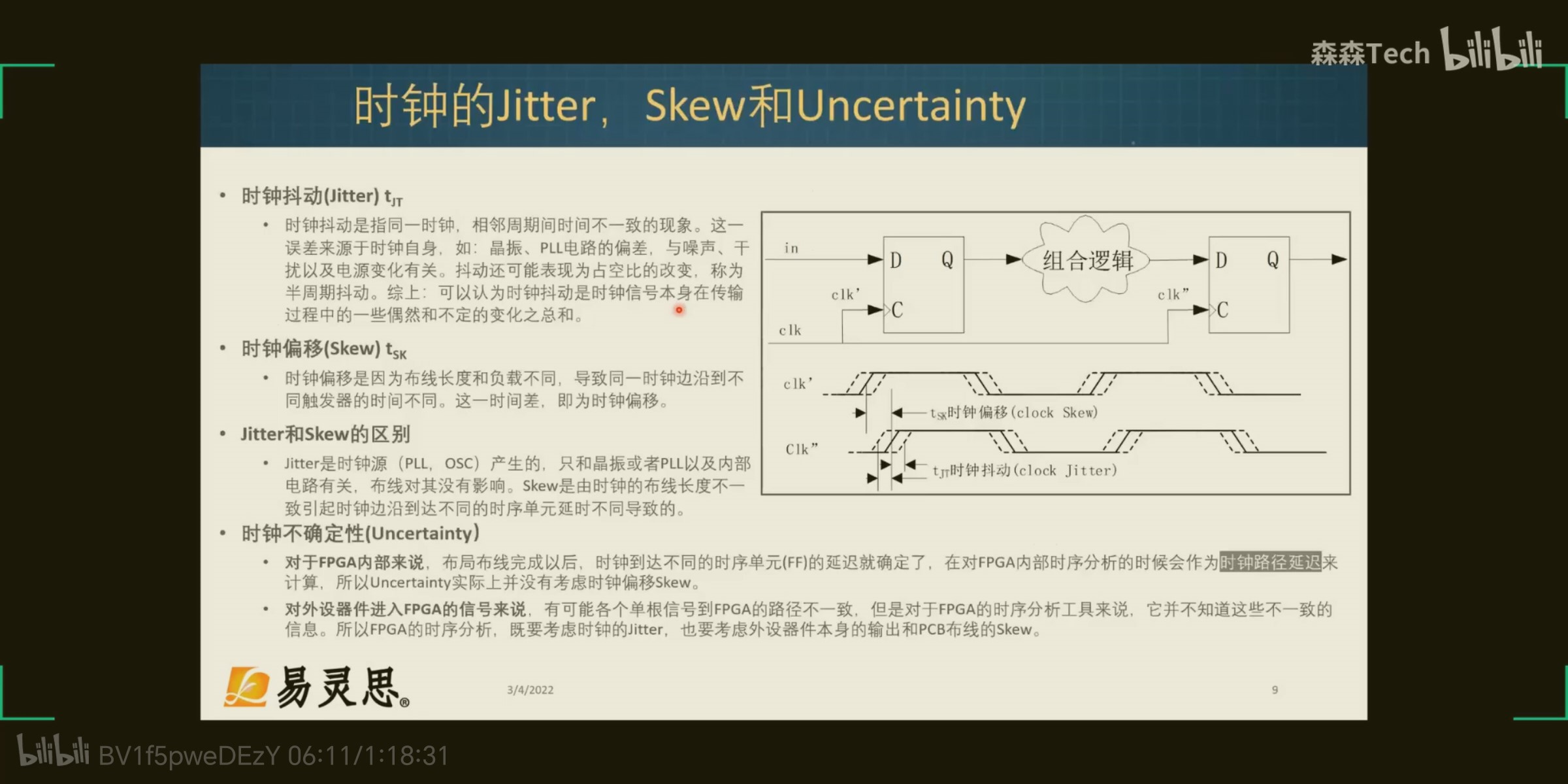

时序相关

1. 数字IC设计之1bit的半加器、全加器实现

笔试 | 数字IC设计之1bit的半加器、全加器实现_1位半加器-CSDN博客

module full_adder1(

input Ai, Bi, Ci,

output So, Co);

assign So = Ai ^ Bi ^ Ci ;

assign Co = (Ai & Bi) | (Ci & (Ai | Bi));

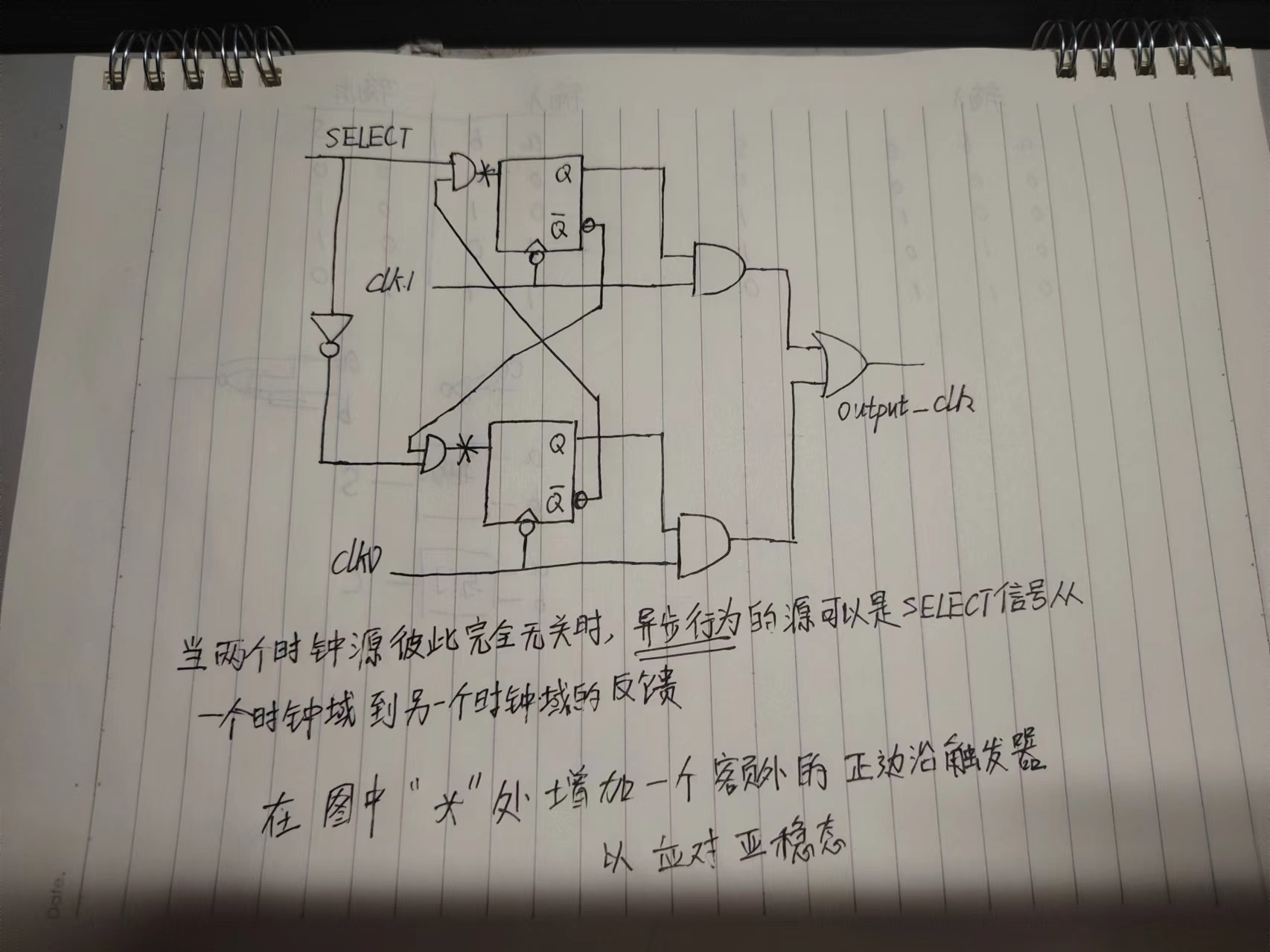

endmodule2. Glitch free 无毛刺时钟切换电路

Glitch free 无毛刺时钟切换电路、时钟无缝切换、时钟无毛刺切换技术_2种时钟无毛刺切换电路设计方案图-CSDN博客

3.相关时钟源的毛刺保护

在时钟的下降沿寄存选择信号(SELECT)可确保在任一时钟处于高电平时输出端不会发生变化,从而防止斩波输出时钟(意思是下降沿寄存,可以保证下降沿到来之前输出端保持不变,这样就不会斩断当前时钟了)

从一个时钟的选择到另一个时钟的反馈使开关能够在开始传播下一个时钟之前等待取消选择当前时钟,从而避免任何毛刺(意思是即使当前SELECT突然变化了,也必须等待到当前时钟的下降沿到来才能去使当前时钟无效,这一段时间就避免了毛刺(glitch))

reg out1;

reg out2;

always @(negedge clk1 or negedge rst_n)begin

if(!rst_n)begin

out1<=0;

end

else begin

out1<=~out0 & select;

end

end

always@(negedge clk0 or negedge rst_n)begin

if(!rst_n)begin

out<=0;

end

else begin

out1<=~select & ~out1;

end

end

assign outclk=(out1& clk1) |(out0 & clk0);

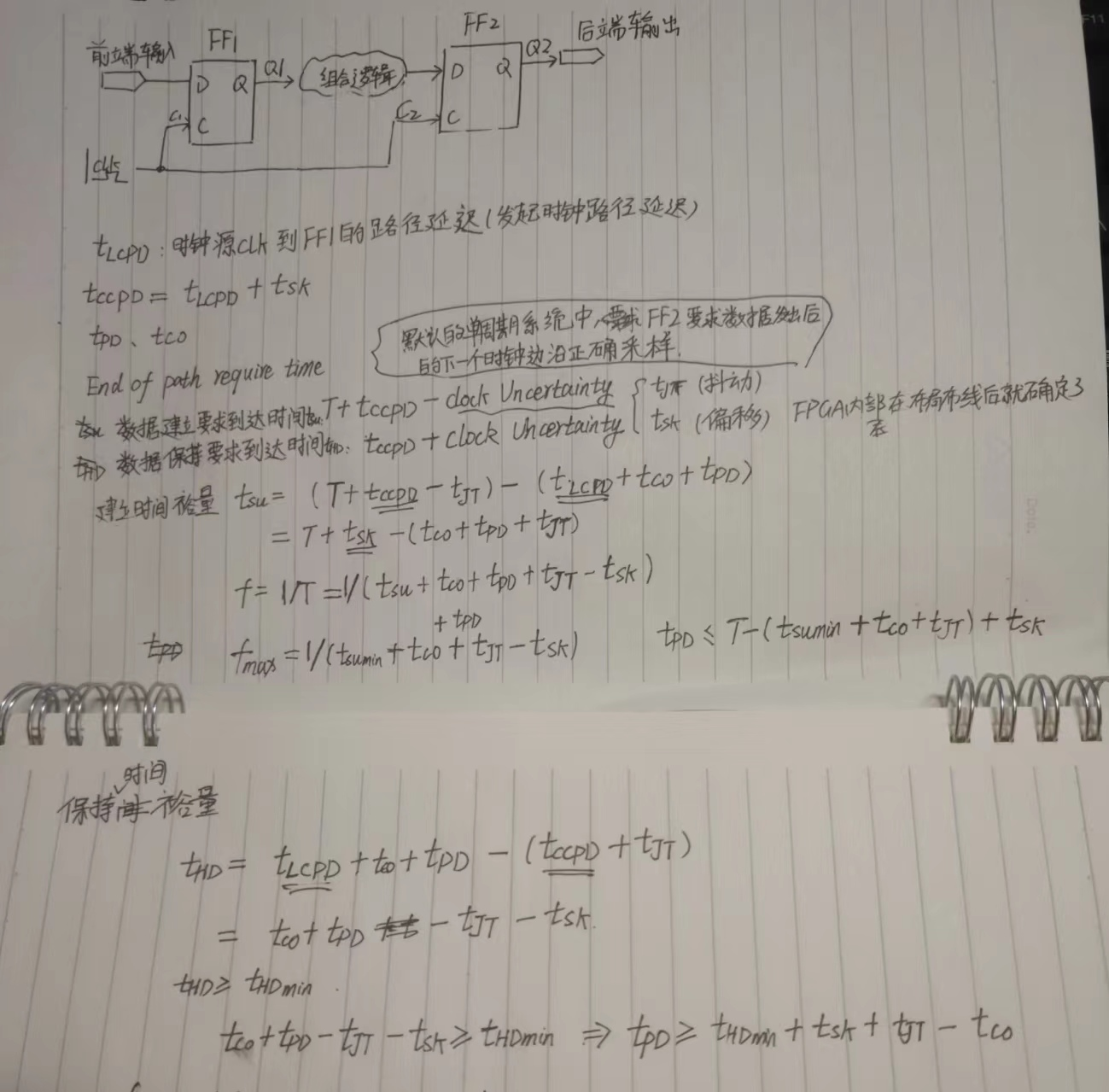

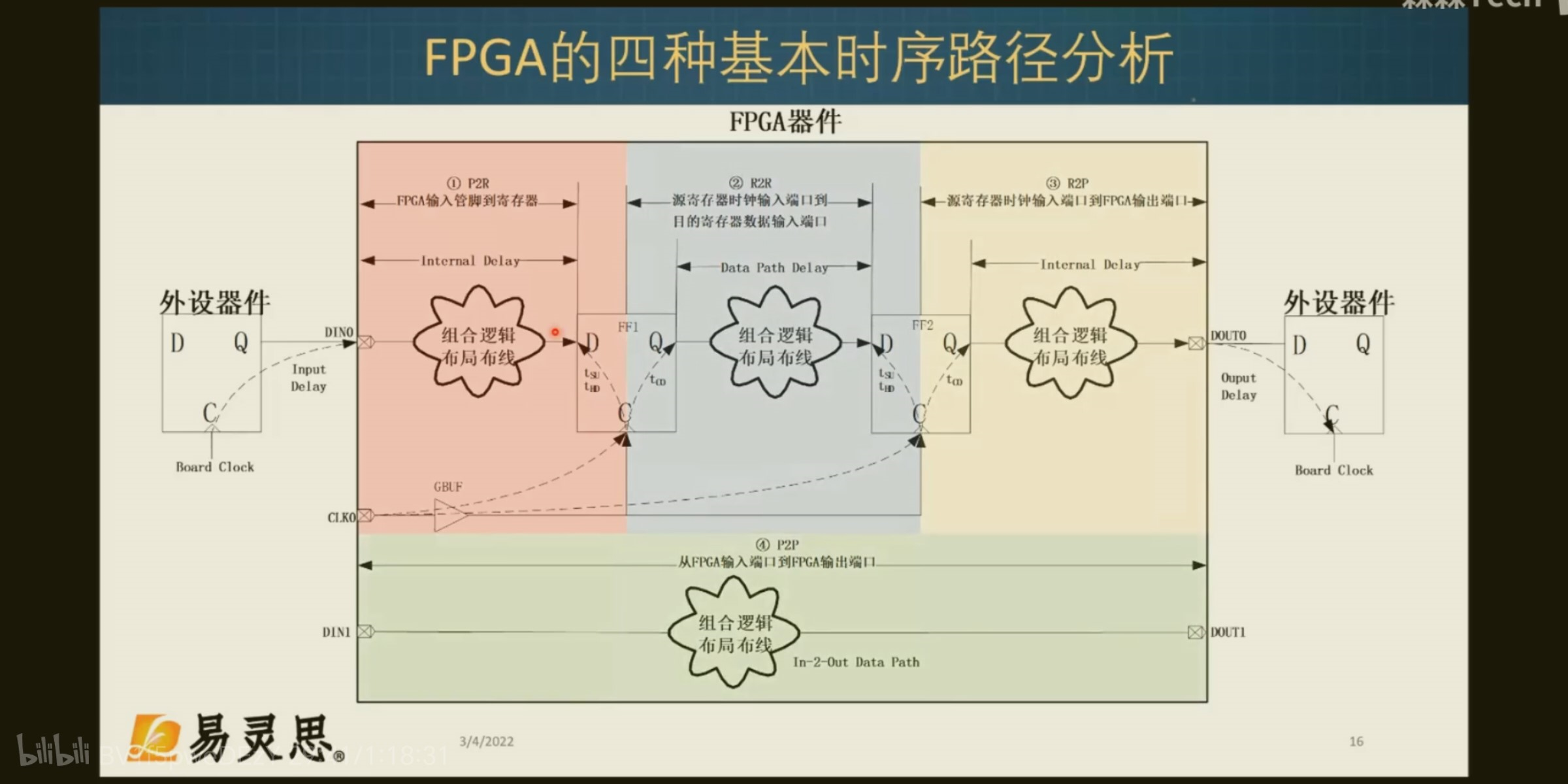

4. 时序逻辑计算

4.1 一道题目(还没明白)

分析一个具体的时序路径(信号从端口A进来,FPGA内部有两个寄存器,然后连接到输出端口B,输出端口B所连接的外围设备有路径传输时延和建立时间的说明,请计算FPGA内部第二个寄存器到输出端口之间的延时T的最大值;端口A的最大输入延时为0.6,端口B的最大输出延时为0.8,时钟周期为2ns,不确定度为0.3

即计算上图中的R2P组逻辑允许的的最大延迟

4.2 相关计算题

https://blog.csdn.net/z951573431/article/details/117411885

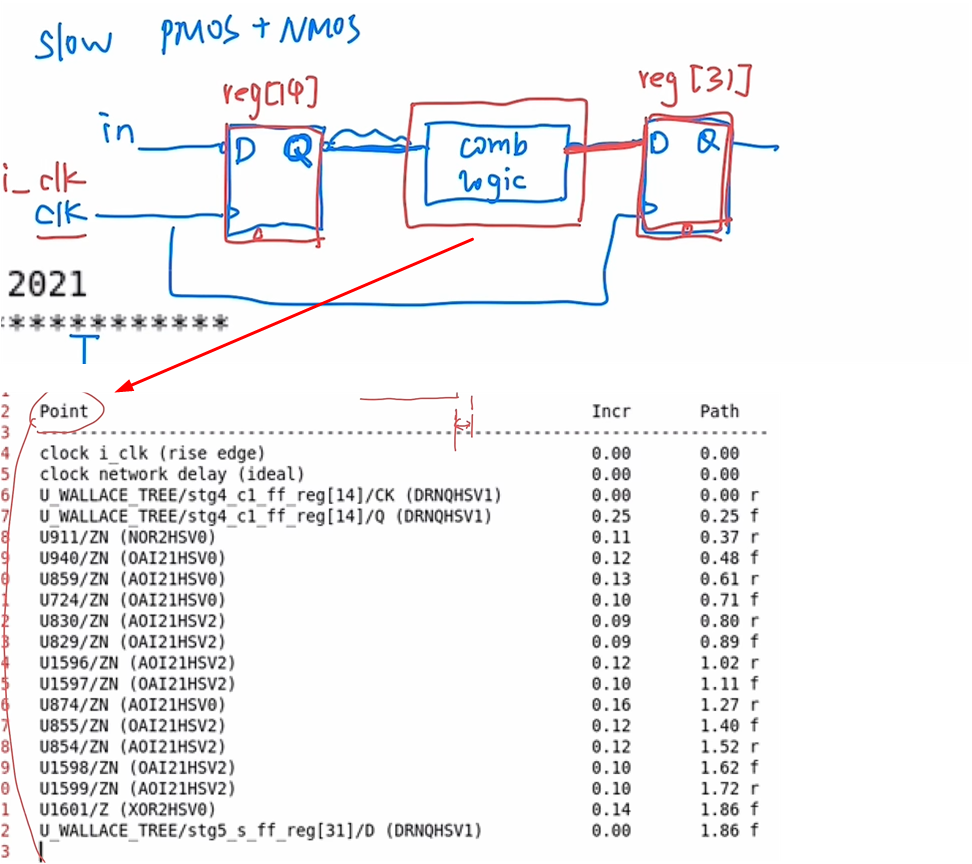

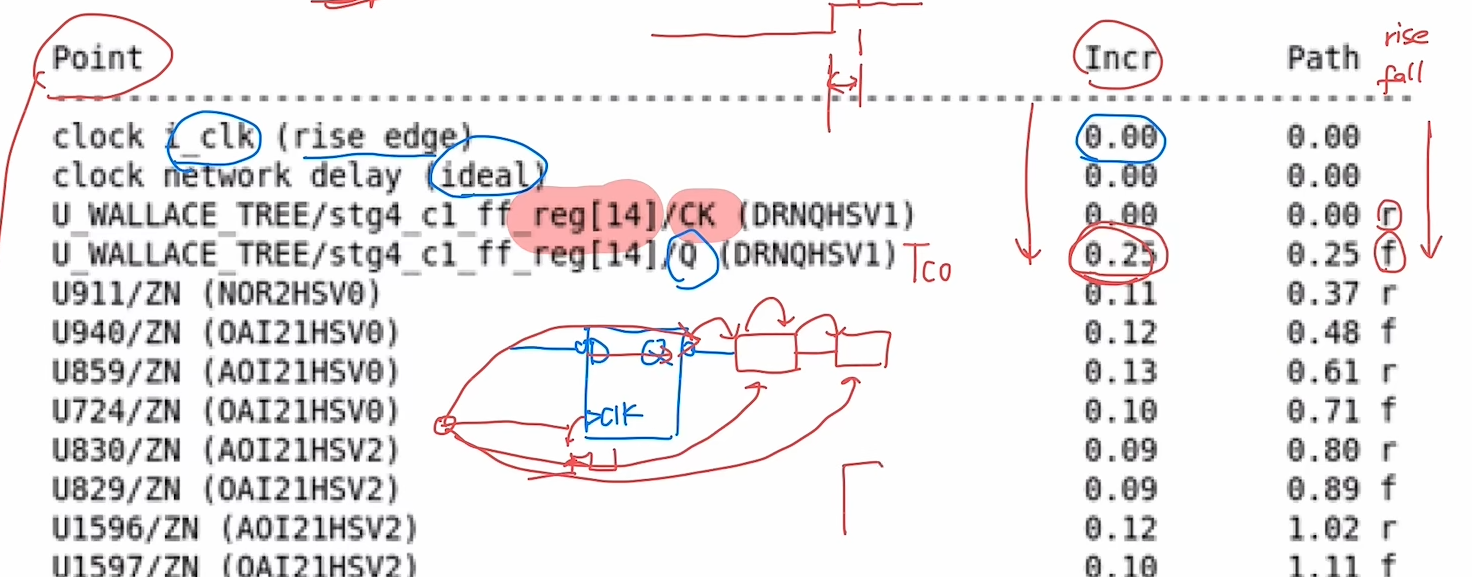

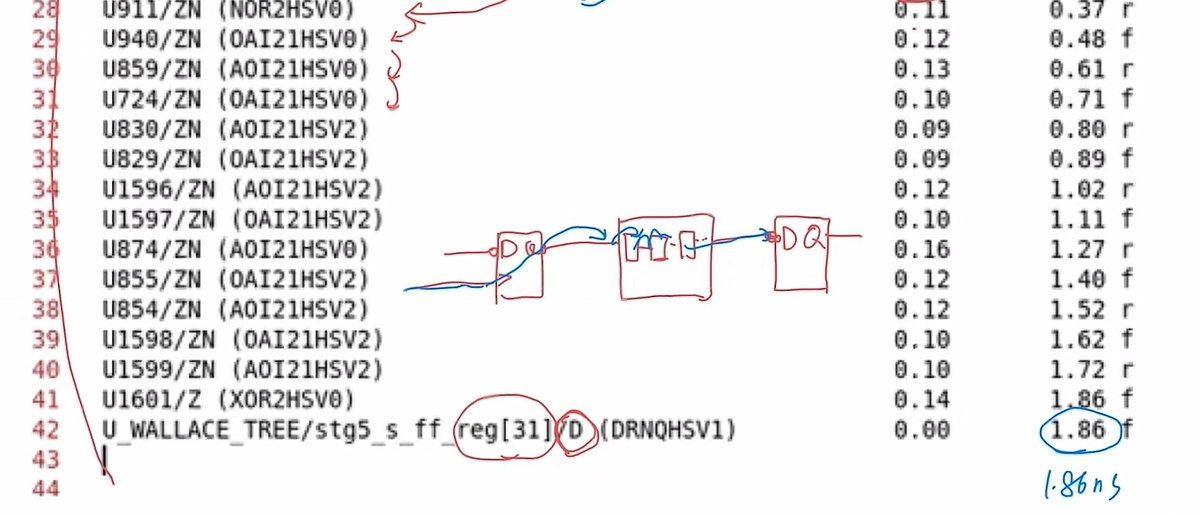

5. 看懂时序报告

https://www.bilibili.com/video/BV1Sg41197UK

5.1 建立时间

5.2 保持时间

5.3 发生时序违例应该怎么办?

- 建立时间不满足

- 降低时钟工作频率,增大T

- 更改组合逻辑部分延迟(Tlogic),插入寄存器,缩短电路逻辑

- 保持时间不满足(和时钟周期无关,改变时钟周期无法改善)

- 改善Tlogic,加入延时缓冲,例如两级反相器

通信、信号处理

1. 信号处理中的时频对偶特性,列出三种

https://blog.csdn.net/weixin_39762348/article/details/110998215

- 卷积定理: 在时域中两个信号的卷积,对应到频域中则是它们频谱的乘积。反之,频域中的卷积对应到时域中则是信号的乘积。这一性质对于滤波和信号的解析非常重要。

- 傅里叶变换的双重性: 傅里叶变换在时域和频域之间具有对偶性。例如,信号在时域的每一个点对应于频域中的一个频率成分,反之亦然。时域中的时间延迟对应于频域中的相位变化,这使得我们可以通过变换更容易地分析和理解信号。

- 时间和频率的互换: 一个信号在时间上越宽,频域中的频谱则越窄,反之亦然。这表明了时间和频率的互换关系,也就是说,一个信号的某些特性可以在两个域中以相反的方式表现出来。这种特性在信号的压缩和重构中也非常重要。

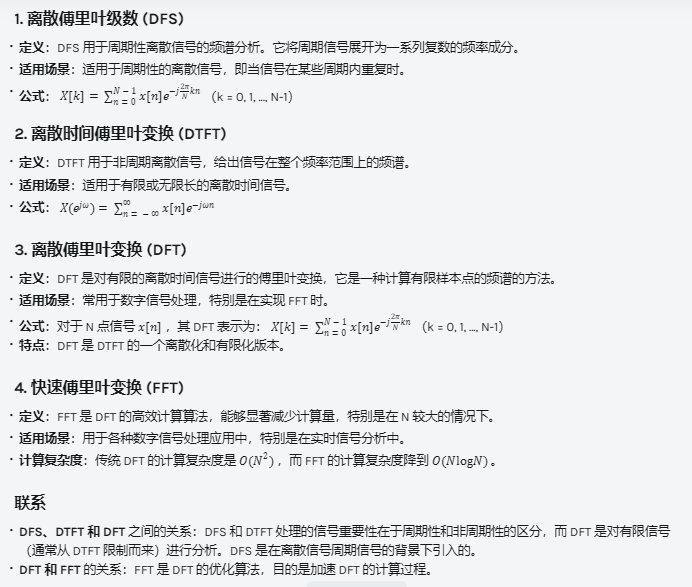

2. 描述 DFS、DTFT、DFT、FFT 的区别与联系

3.频谱分析为什么要加窗?什么时候可以不加窗?

https://blog.csdn.net/s09094031/article/details/105744249

FFT假设输入信号是整数个周期信号。如果输入信号满足条件,则不需要加窗。但实际上这两个条件几乎不能满足,FFT的这个假设会导致频谱泄露,为了减少频谱泄露需要用到窗函数

频谱分析中加窗的主要原因是为了减少由于信号截断引入的频谱泄露和其他失真。下面是详细的解释:

3.1 加窗的原因

- 减少频谱泄露:

- 截取信号时,如果直接使用一个有限的时间段,会导致信号在时域上不连续,产生频谱泄露。这是因为傅里叶变换假定信号是周期的,而如果信号在窗口边缘突然改变,会引入伪频率成分。

- 平滑频谱:

- 加窗可以使信号在窗口边缘处的幅度逐渐减小,平滑过渡,减少高频成分的影响,从而产生更好的频谱估计。

- 提高分辨率:

- 有些窗函数(如汉明窗、黑曼窗等)可以提高频谱的主瓣宽度和副瓣衰减,使得相邻频率成分之间的区分度更高。

3.2 什么时候可以不加窗

- 长时间信号:

- 如果信号的持续时间非常长,且可以被完整捕捉,通常不加窗的影响较小,但仍需考虑实际的采样和截断。

- 稳定信号:

- 对于频率成分非常稳定的信号(例如某些纯正弦波),加窗的影响较小,但实际上加窗仍能提供更准确的频谱。

- 分析目标不敏感:

- 如果对某些具体的频率成分不太敏感,或者只是想获得大致的频谱形状,可能不需要加窗。

- 某些频谱方法:

- 一些频谱估计方法(如自相关法)可能在某些条件下不需要加窗,但这也依赖于具体应用场景

3.3 半带滤波器

https://blog.csdn.net/bleauchat/article/details/85238738

半带滤波器是一种特殊的FIR滤波器,其阶数只能为偶数,长度为奇数。滤波器系数除了中间值为0.5外,其余偶数序号的系数都为0(因此也大大节省了滤波时的乘法和加法运算)

半带滤波器是一种特殊的低通FIR数字滤波器。这种滤波器由于通带和阻带相对于二分之一Nyquist频率对称,因而有近一半的滤波器系数精确为零。

4. DUC 上变频技术/DDC 下变频技术

5. 数据拟合技术

- 请问如何实现对宽带DAC链路的不平坦度进行补偿

- 请问如何实现对宽带射频链路的带内不平坦度进行补偿

5.1. 宽带DAC链路的不平坦度补偿

不平坦度概述: 不平坦度通常指DAC链路在不同频率下信号幅度的变化,可能因DAC特性或其他系统组件引入的非理想行为导致。

实现补偿的步骤:

- 数据采集:

- 收集DAC输出信号的频谱数据,使用频谱分析仪或类似工具,找出不平坦度特征。

- 建模:

- 应用曲线拟合技术(如多项式拟合、样条插值等)生成信号的理论响应曲线,与实际测量结果进行对比。

- 生成补偿曲线:

- 根据拟合结果计算出补偿曲线,即用以对抗不平坦度的补偿信号。

- 信号处理:

- 将补偿曲线应用于DAC输入信号,创建补偿后的信号。在某些情况下,可能需要运用数字滤波器实现这一过程,例如使用FIR或IIR滤波器。

- 验证与调整:

- 反复测试补偿效果,调整补偿曲线以优化输出满足设计要求。

5.2. 宽带射频链路的带内不平坦度补偿

带内不平坦度概述: 带内不平坦度是指射频链路在带内频带内的增益波动,这可能影响信号的质量和传输性能。

实现补偿的步骤:

- 测量与分析:

- 使用网络分析仪或频谱分析仪测量射频链路的增益特性,记录不同频率下的幅度和相位。

- 获取不平坦性特征:

- 通过测量数据,识别不平坦区域并提取其幅度响应特征。可以使用快速傅里叶变换 (FFT) 分析频域特征。

- 设计补偿网络:

- 设计一个补偿网络(如电路中加入滤波器)的增益响应,与不平坦度特征相反,以实现综合补偿。

- 实现补偿措施:

- 根据设计的补偿网络进行实现,可能是数字滤波(如果使用DSP)或模拟硬件电路来补偿信号的增益波动。

- 测试与优化:

- 验证补偿效果,确保链路在整个操作带宽内的增益稳定在设计范围内,如有必要,再次调整补偿设计。

硬件相关

1.对于共基、共集、共射、推挽电路的分析对比(未看)

https://blog.csdn.net/qq_29545231/article/details/80163871

在共射放大电路中,基极电阻 Rb 的主要作用包括:

Rb是三极管的基极偏置电阻,它的作用是为基极一个小的电流,即提供一个合适的工作点,如果没有这个电阻,那么静态工作点将建立不起来,从而造成三极管也工作不了

- 偏置稳定性: Rb与其他偏置电阻一起形成偏置网络,确保晶体管在适当的工作点上以获得线性放大。它有助于维持 biasing 电流,防止因温度变化或晶体管参数变化而导致的工作点漂移。

- 输入阻抗的影响: Rb对输入阻抗有一定影响,增加 Rb 可能会降低输入阻抗,同时会影响输入信号的衰减。因此,设计时需要平衡输入信号的幅度与电路的输入阻抗。

- 交流信号耦合:在交流信号情况下, Rb 可以与其他电路元素形成分压器,影响交流信号的耦合和放大效果。

- 交流增益的影响:在一定程度上, Rb 的值也会影响交流增益,尤其是在高频应用中,需考虑其对增益的影响。

2. 芯片引脚-高阻态

芯片引脚处于高阻态(High-Impedance State,简称Hi-Z)时,实际上是处于类似于“开路”的状态。这意味着引脚既不驱动高电平,也不驱动低电平,而是对外界的电信号没有影响。📡

在这种状态下,其他设备或电路可以在同一引脚上进行信号传输,而不会受到该引脚的干扰。高阻态常用于三态缓冲器、总线系统等场景中。

3.所有LDO都有OCP功能

并不是所有的线性稳压器(LDO)都有过流保护(OCP)功能。

LDO的设计和特性可以有很大的不同,有些型号可能会集成过流保护,以防止在过载或短路情况下损坏设备。然而,也有很多LDO没有这一功能。选择LDO时,建议查阅具体产品的数据手册,以确认其是否具有OCP和其他保护功能。

4. MOSFET用作开关时

5. TTL电路是电流控制,CMOS电路是电压控制?

TTL电路:

- 电流控制:在TTL电路中,逻辑状态是通过电流的流动来控制的。它通常使用双极性晶体管(BJT)来实现逻辑功能。当输入电流通过基极时,BJT被驱动导通,从而允许更大的电流通过收集极与发射极之间。

- 这种电路在高电流状态下工作,相对较快,但功耗较高。

CMOS电路:

- 电压控制:CMOS电路利用互补的P型和N型MOSFET晶体管,其工作原理是通过控制栅极电压来改变MOSFET的导通状态。只有在栅极电压达到一定的阈值后,MOSFET才会导通。

- CMOS电路在静态状态下几乎不消耗电流,因此功耗较低,适合用于低功耗应用。

6. Buck变换器,占空比为D,连续模式下,输出电压和输入电压之比为?

在 Buck 转换器(降压变换器)中,当工作在连续导通模式(CCM)时,输出电压 $ V_{out} $ 和输入电压 $ V_{in} $ 之间的关系可以用占空比 $ D $ 来表示。

因此,输出电压与输入电压之比等于占空比 $ D $。当 $ D $ 的值从 0 到 1 变化时,输出电压会在 0 到 $ V_{in} $ 之间变化。

7. 板噪可用什么种类电容优化噪声?--软端子电容?陶瓷电容?消音电容?电解电容?

在电路设计中,优化板噪声可以使用多种类型的电容,具体选择取决于应用场景和频率要求。以下是几种常见电容的特点和应用:

- 陶瓷电容:

- 适用于高频应用,具有较低的等效串联电阻(ESR)和良好的去耦性能。

- 常用于电源去耦和信号滤波。

- 电解电容:

- 适合低频应用,通常用于电源平滑和去耦。

- ESR相对较高,不适合高频噪声的抑制。

- 消音电容:

- 通常用于低频噪声的吸收和滤波,帮助降低干扰。

- 可以与其他电容结合使用,增强效果。

- 软端子电容:

- 主要用于减少对信号完整性的影响,适合在某些特定应用中使用。

在大多数情况下**,陶瓷电容是优化高频噪声的最佳选择,而电解电容则适用于电源的低频噪声抑制**。

8. Boost 、Buck 、 LDO 、DC-DC分别是?

- LDO:通过线性调节,输入电压和输出电压之间的差异会导致功率损耗,以热量的形式散发。这种方式相对简单,但效率会随着输入和输出电压差距的增大而降低。

- Boost、Buck 和 DC-DC 转换器:这些都是开关式电源转换器,工作效率高,能量通过开关元件调节。Boost 增加电压,Buck 降低电压,DC-DC 是一个总称,包含双向转换。

- Boost 转换器(升压转换器):

- 将输入电压提高到比输入电压更高的输出电压。

- 适用于需要高于输入电源电压的应用,比如电池供电的设备。

- Buck 转换器(降压转换器):

- 将输入电压降低到比输入电压更低的输出电压。

- 常用于提供低电压电源,如从12V降到5V或3.3V的需求。

- LDO(线性稳压器):

- 通过线性调节维持稳定的输出电压,通常用于输入电压比输出电压高的情况。

- 优点是噪声低、设计简单,但效率较低,尤其是当输入电压和输出电压差距较大时。

- DC-DC 转换器:

- 总称, 包含Boost和Buck等,通过开关电源技术实现直流电压的调整。

- 适用于高效能的电源管理需求。

9. PCB走线中,哪种信号无需特别保护?

时钟,SPI,MIPI,中断 信号线

在 PCB 走线中,通常来说,中断信号线相对其他信号(时钟、SPI、MIPI)来说不需要特别的保护。原因如下:

- 时钟信号:时钟信号需要较高的完整性和时序准确性,因此在走线时应注意走线长度和阻抗匹配,避免反射和干扰。

- SPI(Serial Peripheral Interface):SPI 信号也必须保持高完整性和抗干扰能力,以保证数据传输的准确性,尤其是在高速应用中。

- MIPI(Mobile Industry Processor Interface):MIPI 是一种高速接口,要求信号线具有非常好的信号完整性和传输线控制,通常需要差分信号和特定的走线设计。

- 中断信号:尽管中断信号也需要一定的抗干扰能力,但它一般是较低频率的信号,且对时序和幅度的要求相比其他信号较低,因此在 PCB 走线中往往不需要如前述信号那样的特别保护。

10. 放大器的通频带宽度和放大器增益的关系?

11.衡量一个电源的好坏,纹波是一个重要的参数,开关电源这方面是优于线性电源的?对吗?

通常情况下开关电源在纹波控制方面优于线性电源。下面是一些比较的要点,帮助你更好地理解这个问题。⚡️

开关电源(Switching Power Supply)

- 工作原理:开关电源通过快速切换开关元件(如晶体管)来控制电压和电流,从而实现能量转换。

- 纹波特性:由于工作频率高,一般可通过设计滤波器来有效降低纹波。开关电源的输出纹波通常相对可控,且可以使用较小的滤波元件。

- 效率:开关电源的效率通常较高,可以达到80%-90%以上,这意味着在较大的负载下,产生的热量较少,从而减少对系统稳定性的影响。

线性电源(Linear Power Supply)

- 工作原理:线性电源通过调整输出晶体管的导通来实现电压调节,工作方式相对简单。

- 纹波特性:线性电源的输出纹波通常较小,噪声水平低,特别适用于需要高精度和低噪声的应用。然而,线性电源的纹波往往还是受到输入电源质量和设计的制约。

- 效率:线性电源的效率相对较低,尤其是在大电流负载时,因为多余的功率以热量形式损失,导致设备发热。

总结

- 纹波:开关电源通常在处理高频信号和实现较高电流输出时表现更好,能更有效地降低输出纹波。

- 适用场景:虽然线性电源在某些低噪声、高精度的应用中具有优势,但在需要体积小、功率大的场合,开关电源则更具优越性。

12.陶瓷电容两端电压越大,等效容值越小

陶瓷电容的等效容值与其电压有一定的关系,但具体情况取决于电容的类型和材料。通常情况下,陶瓷电容的等效容值会随着施加电压的增加而减小,这种现象称为电压依赖性(voltage coefficient)。

原因:

- 压缩效应:高电压施加到陶瓷电容时,电介质材料可能会受到机械压缩,从而导致电容值下降。

- 材料特性:某些类型的陶瓷电容(例如,多层陶瓷电容,MLCC)在高电压下可能表现出电容值逐渐减小的趋势。这主要与陶瓷材料的特性以及其中的极化效应相关。

实际应用:

- 在选择陶瓷电容时,制造商通常会在数据手册中提供电容的额定值和电压系数,确保在特定工作电压下的性能。

仪器

01.SRAM ,DRAM区别与内存计算

1.简述SRAM,DRAM的区别,电脑上使用的SDRAM颗粒,是属于“SRAM”还是"DRAM"?对于一个SDRAM芯片,其标称值为“,其容量为多少MByte?

SRAM(Static Random Access Memory)和DRAM(Dynamic Random Access Memory)之间的主要区别在于:

- 存储方式:

- SRAM:使用触发器(flip-flop)存储数据,保持数据的方式更为稳定,不需要定期刷新。

- DRAM:使用电容存储数据,数据会随着时间而失去,因此必须定期刷新以保持信息。

- 速度和密度:

- SRAM:速度快,但相对密度低,成本高。

- DRAM:速度较慢,但密度高,成本低。

在电脑中使用的SDRAM(Synchronous Dynamic Random Access Memory)属于DRAM。它是动态随机存取存储器的一种,设计用于与系统时钟同步。

例如一个32MB的SDRAM芯片中有4个Logic-bank(逻辑bank),位宽16bit(即每个单元是16bits),地址线13条,最大行线数13,最大列线数9。计算得:

一个bank的单元数= 2^13 x 2^9= 4194304(即4M)。

芯片总单元数=4Banks × 4M units = 16M units 。

芯片总位数=16M units × 16bits/per_unit = 256M bits 。

芯片总字节数=256M bits/8 = 32M Bytes 。

对应其pdf手册里的“4Banks x 4M x 16Bit”。

02. 施密特触发器的输入和门限关系

施密特触发器是一种具有滞回特性的比较器,广泛用于信号处理。它的输入和门限关系可以总结如下:

- 门限电压:施密特触发器具有两个不同的阈值电压,分别称为:

- 上阈值电压(Vt+):当输入电压超过这个值时,输出会跳跃到高电平。

- 下阈值电压(Vt-):当输入电压低于这个值时,输出会跳跃到低电平。

- 滞回特性:施密特触发器的滞回特性意味着它不会在输入电压接近门限值时频繁切换输出。只有当输入电压越过上阈值(Vt+)时,输出才会变为高;而当输入电压降到下阈值(Vt-)时,输出才会变为低。这种特性可以有效消除信号干扰和抖动,提供更稳定的输出。

- 输入-输出关系:

- 当输入电压 VinVin 小于 Vt−Vt− 时,输出 VoutVout 为低电平。

- 当输入电压 VinVin 超过 Vt+Vt+ 时,输出 VoutVout 为高电平。

- 在 Vt−<Vin<Vt+Vt−<Vin<Vt+ 的区域,输出保持不变。

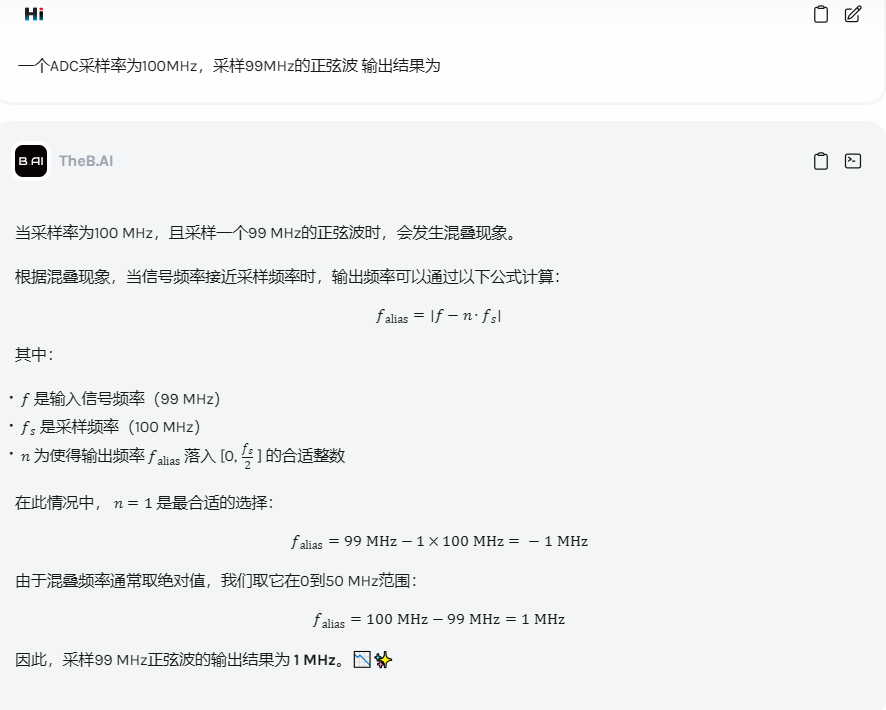

03. ADC采样正弦波

一个ADC的采样率为 100M Sa/s,分别采集 1MHz, 49MHz, 99MHz, 101MHz的正弦波,其输出频率为?

04. 正弦信号通过LHF

幅度为1V,频率为20MHz的正弦波,其通过LHF(低通滤波器,其-3dB带宽为20MHz),则输出信号的幅度和频率为?另外,请介绍一下低通滤波器的关键参数

04-1:输出信号的幅度和频率

- 输入信号:幅度为1V,频率为20MHz

- 低通滤波器的截止频率:20MHz

- 输出幅度:1V ×× 0.707 ≈ 0.707V

- 输出频率:仍然为20MHz

因此,输出信号的幅度约为0.707V,频率仍为20MHz。

04-2:低通滤波器的关键参数

- 截止频率(-3dB频率):

- 这是低通滤波器能够通过的最高频率。超过此频率的信号幅度将迅速减少。

- 带宽:

- 带宽指的是从0Hz到截止频率之间的频率范围。通常,带宽和截止频率是相同的概念。

- 阻带衰减:

- 表示超出截止频率后,信号幅度的衰减程度。通常用分贝(dB)表示,如-20dB/decade表示每增加一个频率倍数,信号衰减20dB。

- 相位响应:

- 滤波器对不同频率信号的相位偏移。低通滤波器通常在低频信号中保持相位,而高频信号则可能发生显著的相位偏移。

- 通带内的增益:

- 通常低通滤波器在截止频率以下保持近似0dB的增益,即通过信号几乎没有衰减。

- 阶数:

- 阶数决定了滤波器的陡峭度。阶数越高,截止频率处的坡度越陡,信号的过渡更为快速。

05. 针对模拟信号的ADC采样,其频谱表示为?

模拟信号的ADC(模数转换)采样后的频谱表示可以用奈奎斯特定理来理解。根据该定理,如果对一个频率为 fmfm 的模拟信号进行采样,采样频率 fsfs 必须至少是最高频率 fmfm 的两倍,即:

fs≥2fmfs≥2fm

ADC采样后的频谱

- 采样后的频谱:

- 进行ADC采样后的频谱会出现反复的镜像,频谱的重复间隔为采样频率 fs 。这意味着在频谱中存在多个以 fs 为周期的镜像。

- 主频谱(基带频谱):

- 原始模拟信号的频谱将在0到 fm 的范围内存在。

- 镜像频谱:

- 如果采样频率 fs 高于 2fm ,那么原信号的频谱在0到 fm 范围内的内容可以在频谱中被保留,而镜像信号则是在 fs ± fm 、2fs ± fm 等位置出现。

- 混叠效应:

- 如果采样频率低于 2fm ,则会出现混叠现象,导致高频信号在低频部分重叠,从而失去信息。

06 二进制和格雷码

请给出二进制和格雷码的相互转换关系,以及0~15十进制数所对应的二进制和格雷码

格雷码转二进制码的基本思路:格雷码转二进制是从左边第二位起,将每位与左边一位二进制码的值异或,作为该位二进制码后的值(最左边一位依然不变)。

assign bin[i] = bin[i + 1] ^ gray[i]; //格雷码与二进制数前一位进行异或逻辑运算二进制码转格雷码的基本思路:从最右边一位起,依次将每一位与左边一位异或(XOR),作为对应格雷码该位的值,最左边一位不变。

assign gray= bin ^ (bin>>1);| 十进制 | 二进制 | 格雷码 |

|---|---|---|

| 0 | 0000 | 0000 |

| 1 | 0001 | 0001 |

| 2 | 0010 | 0011 |

| 3 | 0011 | 0010 |

| 4 | 0100 | 0110 |

| 5 | 0101 | 0111 |

| 6 | 0110 | 0101 |

| 7 | 0111 | 0100 |

| 8 | 1000 | 1100 |

| 9 | 1001 | 1101 |

| 10 | 1010 | 1111 |

| 11 | 1011 | 1110 |

| 12 | 1100 | 1010 |

| 13 | 1101 | 1011 |

| 14 | 1110 | 1001 |

| 15 | 1111 | 1000 |

面试中的问题

对一,二面过程中遇到的问题和不足之处进行分析

如果代码中发现了BUG,该如何解决?

应该保留模块的自检功能,从源头定位问题

有接触过跨时钟域的处理吗?

描述一下AXI4-Lite 的读操作完整过程

当你发现时序违例时,如何排查问题,是否有过观察某一个完整信号路径的过程?如果你所设计的模块在高频下无法正常工作,你处理过吗?

举个例子:一个周期内同时计算了多个数的复数乘法等复杂运算,如何保证其结果正确

一个信号路径的报告具体长什么样子(没接触过,看视频记不住)

“若是做工程师实现代码,代码量重要”

时序综合报告出现了问题,你怎样处理?你遇到过吗?

进行的Matlab和Verilog仿真验证,有使用标准化的流程吗(Cmodel,测试向量什么的)

在代码中定义了 reg和wire,那么reg综合出来一定是寄存器类型吗?

https://www.cnblogs.com/wenhaoele/p/5183144.html

在设计中,输入信号一般来说你是不知道上一级是寄存器输出还是组合逻辑输出,那么对于本级来说就是一根导线,也就是wire型。而输出信号则由你自己来决定是寄存器输出还是组合逻辑输出,wire型、reg型都可以。但一般的,整个设计的外部输出(即最顶层模块的输出),要求是寄存器输出,较稳定、扇出能力也较好。