OFDM-802.11a

OFDM-802.11a

1. 相关文章

书籍:基于XILINX FPGA的OFDM通信系统基带设计 (史治国,洪少华,陈抗生)

2. 相关仿真及代码

github:

GitHub - jhshi/openofdm: Sythesizable, modular Verilog implementation of 802.11 OFDM decoder.

GitHub - phthinh/OFDM_802_11: IEEE 802.11 OFDM-based transceiver system

论文:基于FPGA部分重构的端到端多标准OFDM收发器架构[1]

GitHub - FlyHighInSky/OFDM-on-FPGA:一个OFDM的matlab及verilog实现

微信专栏:

OFDM 802.11a的FPGA实现:发射部分的最终实现(含完整工程文件)

https://mp.weixin.qq.com/s/cw2M4kx4y6PA18Qrnj1Dow

OFDM-同步:

对于一个通信系统而言,必须哟啊考虑如下的一些同步问题,如接收机不知道符号的定时起始位置、发射机和接收机的载波频率存在偏差、发射机和接收机的采样频率不完全相同等。

OFDM系统中主要有以下三个方面的同步要求:

- 时间同步,包括帧的检测和符号同步,以保证正确检测到新数据的到达,并保证IFFT和FFT起止时刻一致;

- 载波同步,要消除接收机的本振频率与发射机本振频率和相位的偏差引起的系统性能的降低

- 采样时间同步,消除接收机和发送机在进行数模/模数变换时采样频率不一致引起的偏差

OFDM-频率选择性信道的均衡也是一个关系到系统性能的重要性问题。

相关代码

GitHub - NeilJudson/OFDM_Synchronization: both Matlab and Verilog.

https://www.researchgate.net/file.PostFileLoader.html?id=58c8d0fd48954c6518289310&assetKey=AS%3A472045004824576%401489555707409

Design and FPGA Implementation of OFDM System with Channel Estimation and Synchronization:https://spectrum.library.concordia.ca/id/eprint/977626/

BOOK-read:

IEEE 802.11a 物理层协议(1999-WIFI-2)

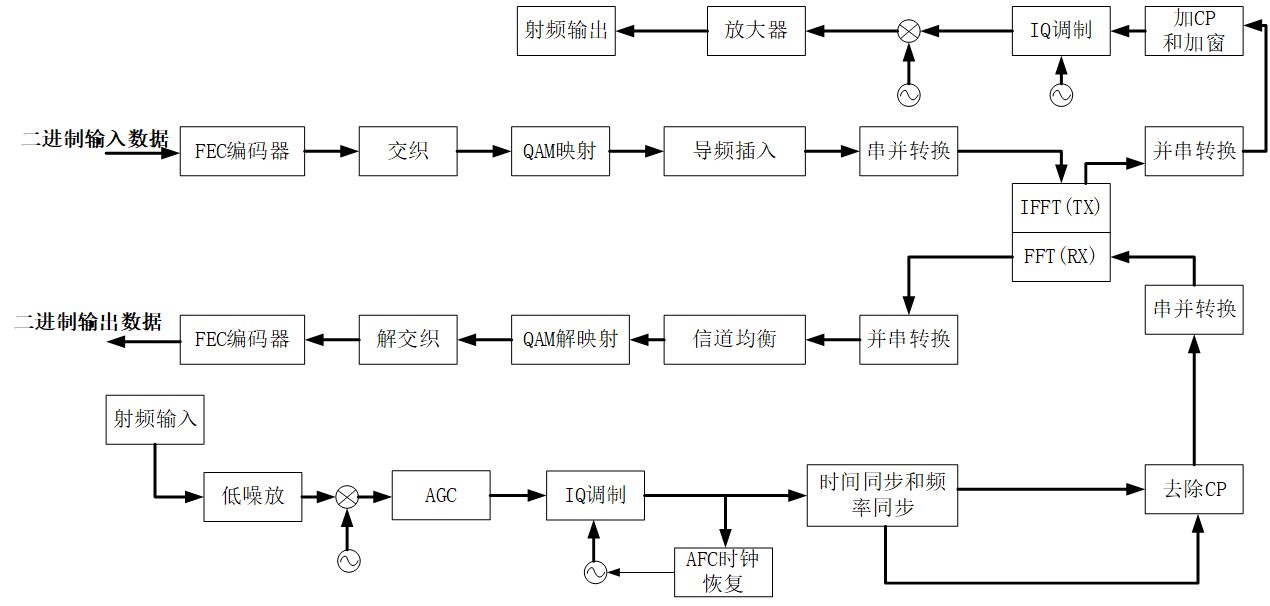

原理框图及参数

https://blog.csdn.net/Flag_ing/article/details/136419920

| 参数 | 数值 |

|---|---|

| 数据速率(Mb/s) | 6,9,12,18,24,36,48,54 |

| 调制方式 | BPSK、QPSK、16QAM、64QAM |

| 编码效率 | 、、 |

| 子载波数量 | 52 |

| 导频数量 | 4 |

| OFDM符号长度() | 4 |

| 保护间隔长度() | 800 |

| 子载波间隔(kHz) | 312.5 |

| 信号带宽(MHz) | 16.66 |

| 信道间隔(MHz) | 20 |

其他参数以保护间隔长度为基础进行定义。

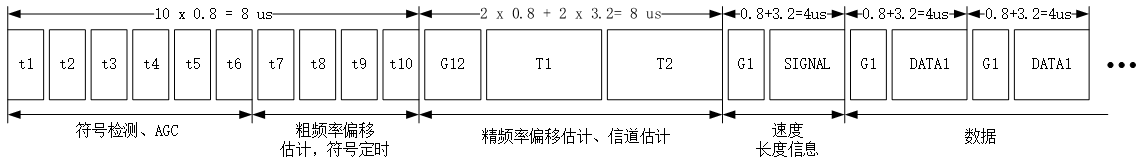

物理层协议数据单元(PPDU)帧结构

子载波的使用

共53个子载波

编号k=0 直流子载波上不传输符号

采用基于的IFFT算法,故点数为64

分别在编号低端和高端留有6个和5个空符号,即

这样可保证系统的子载波频谱集中,从而使得系统占用的频谱带宽尽可能窄,从而使得系统占用的频谱带宽进坑能的窄,以节约频谱资源,减少信道间干扰

OFDM 基带处理器总计架构

1.策略与设计流程

调试策略:

随机二进制比特生成器-->Maltab OFDM仿真

FPGA上实现OFDM基带发射机和接收机

两者进行比较

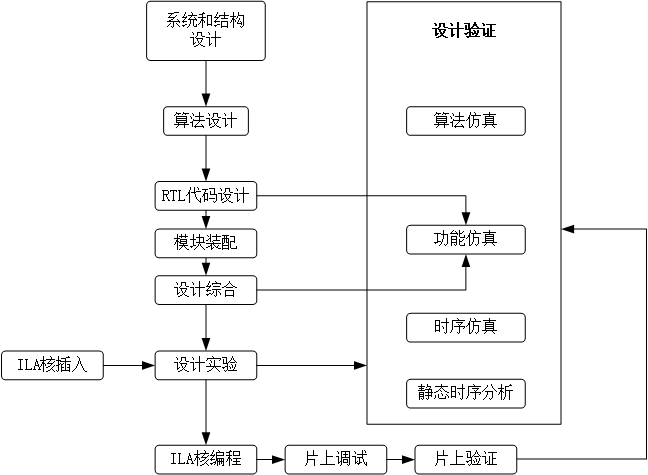

基带处理器的FPGA设计流程:

802_11_a_FPGA_design

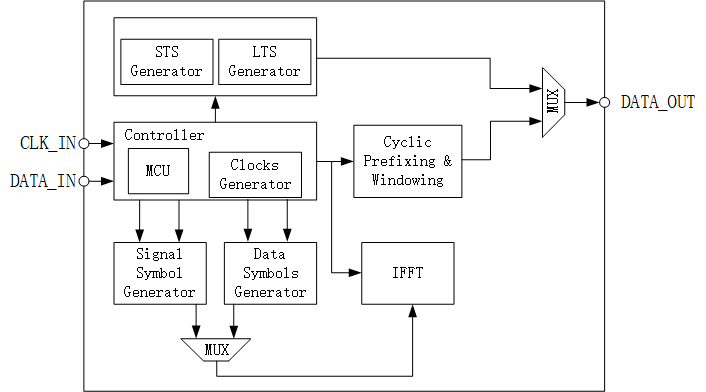

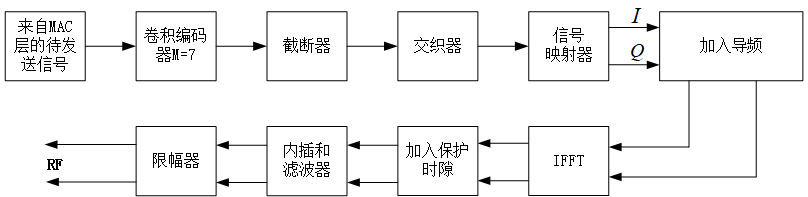

2.发送机总体结构

数据通道:按照一定时序,对数据流处理,生成一个标砖的OFDM符号PPDU

训练序列生成模块(Traning Sequences Generator,TS Generator)

Signal符号生成模块 (Signal Symbol Generator)

Data符号生成模块(Data Symbols Generator)

IFFT 处理模块

循环前缀添加与加窗处理模块(Cyclic Prefixing & Windowing Module)

控制部分:要求各个模块彼此协调,精确同步。

主控单元(Master Control Unit,MCU)

时钟生成模块(Clocks Generator)

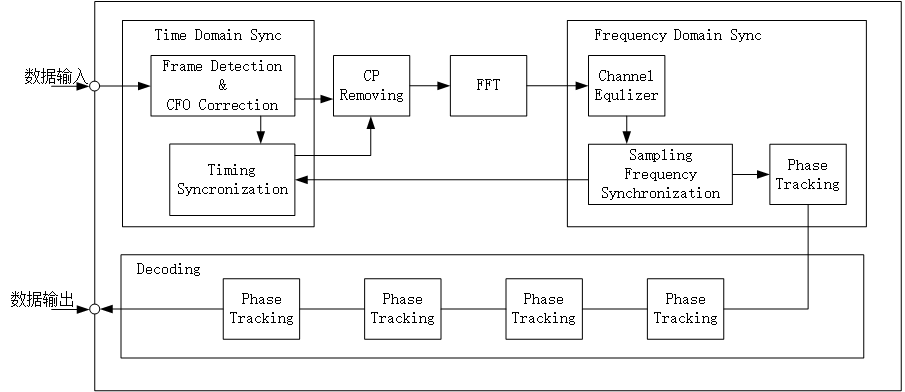

3.接收机总体架构

整个接收机可以分为“同步(Synchronization)”和“解码(Decoding)”两大部分。

同步部分:

- 时域进行的同步处理:

- 帧检测和载波频偏校正模块(Frame Detection & CFO Correction)

- 时间同步模块(Timeing Synchronization)

- 循环前缀去除模块(CP Removing)

- FFT处理模块

- 频域进行的同步处理:

- 信道均衡模块(Channel Equalizer)

- 剩余相位跟踪模块(Phase Tracking)

- 采样频率同步模块(Sampling Frequency Synchronization,SFS)

- 时域进行的同步处理:

解码部分:完成同发送机相反的逆处理

解映射模块(De-mapper)

解交织模块(De-interleaver)

维比特解码模块(Viterbi Decoder)

解扰码模块(De-scrambler)

4.基带处理器-工作时钟

IEEE802.11a标准,一个OFDM的符号的长度为,其中共有80个采样点,则对于64点的处理模块而言,要求其工作频率满足在时间内输出64个样值,及工作时钟频率为。

--->整体基带处理器的系统时钟SYS_CLK

调制方式为16QAM,故而四个输入比特对应一组调制后的I/Q链路数据,若使得调制后输出为20MHz,则输入数据需要20MHZ x 4 =80 MHz (CB_CLK)的时钟。

考虑编码效率为3/4,则在编码和截断之前的数据速率应为(DIN_CLK);MAC层送往物理层的数据为字节格式,物理层处理时要首先进行8位并串变换,因此MAC_CLK作为MAC层时钟的大小为60MHz/8=7.5MHz。

发送端的工作时钟:

时钟名称 时钟频率(MHz) MAC_CLK 7.5 SYS_CLK 20 SYS_CLK_D 40 DIN_CLK 60 CB_CLK 80 接收端的工作时钟:

时钟名称 时钟频率(MHz) clk 20 clk40m 40 clk60m 60 clk80m 80

5. 数据格式

硬件平台上系统内所有复数类型的信号统一使用8位二进制形式(8-bit Signed Binary)表示,由于所有复数数据(训练序列和经过PSK、QAM调制的输出)在频域的值均在,故而规定8位数据的格式为

- s,1,6

- 1位符号位(Sign Bit)

- 1位整数位(Integer Bit)

- 6位小数位 (Franction Bit)

OFDM 发射机设计与实现

1.训练序列的产生

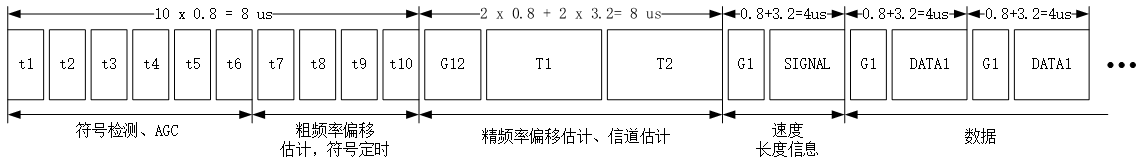

短训练序列:进行信号检测、自动增益控制(AGC)、符号定时和粗频率偏差估计。其包含10个重复的符号,每个长度为800ns。

长训练序列:进行精确的频率偏差估计和信道估计。其长度为8us,包含两个有效OFDM富豪的长度(每个3.2us)和一个长型保护间隔的长度(1.6us)。

生成方法: 将确定的时域样值存在片内存储器中,发送时只需按规定的时序读出即可,不用再进行IFFT变换。

2. 发射机Symbol生成过程

生成PLCP的前导部分

生成PLCP报头,即Signal域信号

生成Data域信号

3.扰码模块

数字通信中,若出现长的”0“或”1“序列,将会影响位同步的建立与保持。在发射机中使用扰码,可以避免这种数据对于接收机定时的不利影响。

为限制电路中存在的不同程度的非线性特性对其他电路通信造成的串扰,要求数字信号的最小周期足够长。

--->将数字信号变换成具有近似于白噪声统计特性的数字序列

加扰:不用增加冗余而搅乱信号,建立在基于反馈移位寄存器序列(或伪随机序列)理论上。

4.信道编码

OFDM 接收机同步

分组交换网络例如无线局域网(WLAN)等,数据的传输带有突发性。

- WLAN系统往往采用突发同步(burst synchronization)的方式,即在分组开始发送之后很短时间内获得同步,这由WLAN系统本身分组交换的特性以及比较高的数据传输速率的要求所决定的,同时为了提高系统吞吐量,还必须保证接收机中用于训练的开销达到最小。

- 前导序列的长度和内容都是经过精心设计的

- 假定信道脉冲响应在数据突发器件没有发生显著变换的前提下设计的

1.IEEE 802.11a中的同步

- 定时同步

- 帧(分组)同步:确定数据分组的起始位置

- 符号同步:目标在于正确的定出OFDM符号数据部分的开始位置,以进行正确的FFT操作

- 载波频率同步

- 检测出频率偏移,然后加以补偿

- 采样时钟同步

- 消除收发端 D/A、A/D采样的频率、相位偏差对系统性能的影响

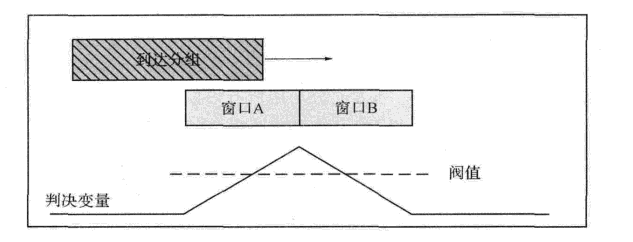

2. 分组检测

分组检测是找寻数据分组起始的近似估计,是接收机工作的第一步。

即 检测突发传输方式的信道上是否由新的数据大大,其算法的好坏直接影响接收机后续的工作

建立假设:(一般将判决变量与预定阈值比较)

: 没有出现数据分组

: 出现分组

2.1 常用算法

- 接收信号能量检测

单滑动窗口能量检测:预定阈值难以确定,需根据接收信号的能量而定。

在每一个时刻n,求和会加入一个新的数值同时丢弃一个旧的数值。移动递归求和计算表达式为

- **双滑动窗口能量检测:**通过计算两个连续滑动窗口的接收能量的比值作为判决变量

计算窗口A,B内的能量,有

理想情况下,

- 利用前导结构进行分组检测

一般通信系统的工程原则是接收机要充分利用所有可以利用的信息

利用前导中短训练符号的周期性,称为延时相关算法

延迟相关值计算为

表示当前接收到的L个数据同D个时刻前的接收到L个数据进行互相关。

接收信号能量的值可表示为

则延时相关算法的判决变量为

上式中 ,即为短训练序列的长度(周期)。

在低信噪比条件下,判决变量可能受到信道中较大随机噪声的影响而超过预先设定的门限值。

通过设置判决变量要在预设门限值之上保持一定的采样周期数的对这种情况有缓解。

2.2 延时相关加长度保持算法的硬件结构

判决条件为:

上式中,做如下近似与简化实现处理:

对于,则有

由于值为事先确定,同时基于仿真结果,设其为,则判决条件表示为

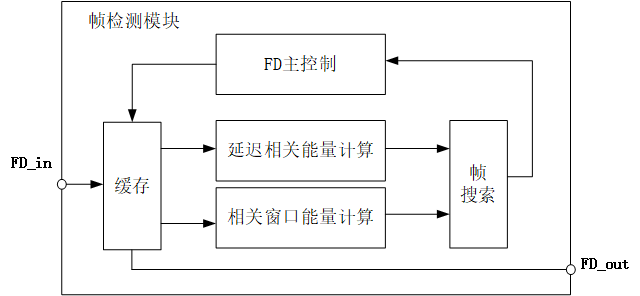

- 数据缓存:事先对等待检测的输入数据进行缓存,同时在找到数据分组和起始的结束位置时,事先对于缓存数据的输出与停止

- 主控制模块:根据系统的当前状态(如分组检测处理过程中、分组检测处理已完成等)以及帧搜索模块的输出结果,向数据缓存模块输出相应的控制指令(分组检测有效,分组检测处理完成有效等)。

- 延迟相关能量计算、相关窗口能量计算和帧搜索:构成延迟相关算法主题,完成分组检测,并反馈给主控制模块。

1.数据缓存(Data Buffer)模块

2.延时相关能量计算模块

T. H. Pham, S. A. Fahmy and I. V. McLoughlin, "An End-to-End Multi-Standard OFDM Transceiver Architecture Using FPGA Partial Reconfiguration," in IEEE Access, vol. 5, pp. 21002-21015, 2017. [doi: 10.1109/ACCESS.2017.2756914]( ↩︎