02.数字电路

02.数字电路

一、基础概念

1.逻辑门

| 名称 | 英文 | 表达式 |

|---|---|---|

| 与 | AND | Y=A & B |

| 或 | OR | Y=A |

| 非 | NOT | Y=~A |

| 与非 | NAND | Y=~(A&B) |

| 或非 | NOR | Y=~(A|B) |

| 异或 | XOR | Y=A^B |

| 同或 | XNOR | Y=(A)&(B) | A&B |

- 组合电路:任意时刻的输出仅取决于该时刻的输入,与电路原来状态无关。

- 时序电路:输出不仅取决于当前时刻的输入信号,而且取决于电路的原来状态。

2. 组合逻辑电路

- 多路选择器:多输入单输出

- 译码器:多输入多输出

- 38译码器:通过输入3个信号组成二进制的8种情况来控制对应输出8bit的8种不同状态

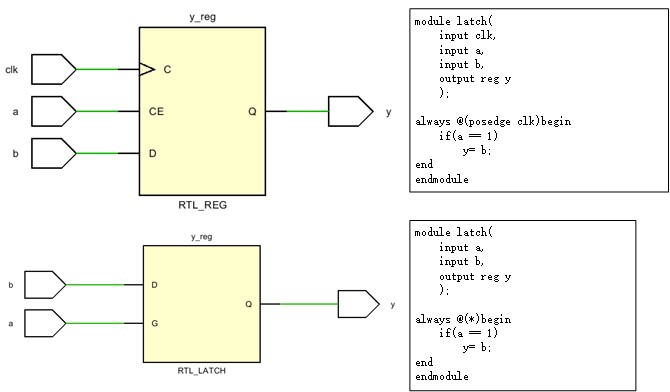

3. 锁存器

参阅:https://blog.rvalue.moe/structure-and-design-of-latches-and-flip-flops/

Latch是时序逻辑,有数据存储功能

锁存器(Latch)是一种对脉冲和电平敏感的存储单元电路,可以在特定输入脉冲或电平作用下改变状态。

锁存,即把信号暂存以维持某种电平状态。

- 数据存储的动作取决于输入时钟(或者使能)信号的电平值,只有当锁存器处于使能状态,输出才会随数据输入发生变化。

- 锁存器不同于触发器,锁存器在不锁存数据时,输出端的信号随输入信号变换,如同通过一个缓存器一样。

- 锁存器分类有:SR锁存器、门控RS锁存器和D锁存器......。

在绝大多数设计中我们要避免产生锁存器。它会让你设计的时序出问题,并且它的隐蔽性很强,新人很难查出问题。锁存器最大的危害在于对电平信号敏感,容易产生毛刺和影响工具进行时序分析, 这对于下一级电路是极其危险的。所以,只要能用触发器的地方,就不用锁存器。

锁存器没有时钟信号,只有数据输入和使能以及输出Q端,没有时钟信号也就说明我们没有办法对这种器件进行时序分析,这个在时序电路里面是非常危险的行为,因为可能引起时序不满足从而导致电路功能实现有问题 。

产生Latch的情形:

- 只有不带时钟的 always 语句的 if 或者 case 语句不完整才会产生 latch,带时钟的语句 if 或者 case 语句不完整描述不会产生 latch。

- 信号的自我赋值

https://mp.weixin.qq.com/s/Yn-wpyZ33DJXwCUTnCWDmA

4.触发器

触发器类似受到时钟控制的锁存器, 其中有一个输入被连接到同步的时钟, 并且触发器在特定时钟时刻会对输入有不同的响应。

交叉耦合的门构成的双稳态的存储原件称为触发器。分为上升沿触发和下降沿触发。可以认为是两个不同电平敏感的锁存器串连而成。前一个锁存器决定了触发器的建立时间,后一个锁存器则决定了保持时间。

eg.主从D触发器

触发器的串联与并联

4.1 T触发器

https://blog.csdn.net/qq_45766606/article/details/129446937

附1:锁存器latch和触发器FF

Flip-Flop是触发器(简写为FF),边沿触发,可以用作寄存器register存储数据;Latch是锁存器,电平触发,也可以存储数据。

优缺点

发器比锁存器占的面积大,但是一般在应避免产生Latch,原因如下:

(1)Latch是**电平触发,对毛刺敏感**;Flip-Flop是边沿触发,稳定性高; (2)Flip-Flop可以设计成均在同一个时钟的同一个边沿的驱动下触发,是同步电路设计,而如果这其中有Latch的产生,则数据的寄存不止发生在某一边沿,打破了同步设计(异步设计),**这样不利于STA静态时序分析**(STA只能分析同步电路,插Latch以后属于异步)。什么情况下产生latch

因为在组合逻辑中想实现的是组合逻辑,却因为条件不完备没有给出else...条件下要执行的赋值,所以此时默认保持输出不变,这样就隐含了数据暂存在里面,所以产生了Latch来暂存数据。

1)在组合逻辑中,if...else条件不完备;

2)在组合逻辑中,case 语句不完备;

在时序逻辑中,即使if...else或者case不完备,默认会用FF来实现数据的存储。

5.寄存器

寄存器一般由多个触发器构成

6. 计数器

基于寄存器的一种简单运算

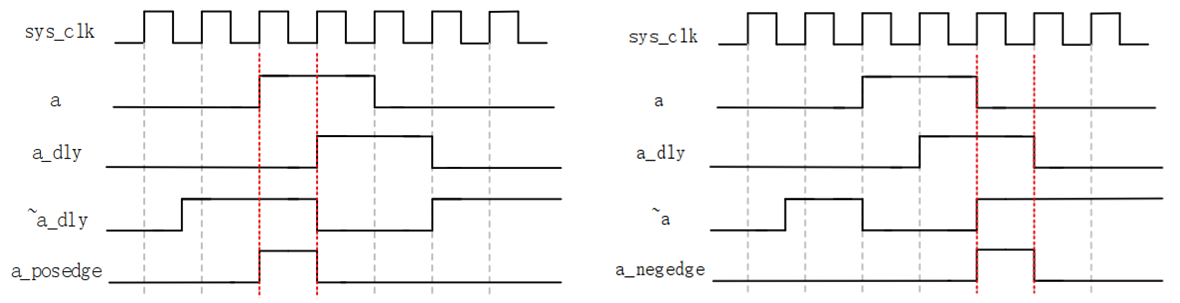

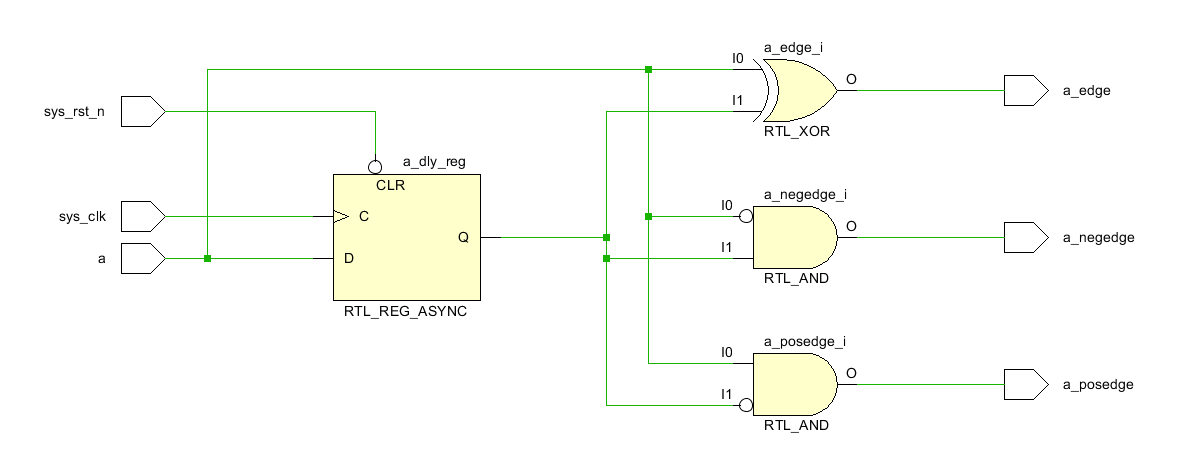

7. 边沿检测电路

边沿检测指的是检测一个信号的上升沿或者下降沿,即产生一个脉冲信号。

在复杂的逻辑设计中,很多情况我们都需要检测信号的跳变,以控制其他信号的动作

8. 分频器电路设计(未完)

一种方式是直接使用PLL进行分频,但是这种分频有时候受限于 PLL 本身的特性**,比如输入 100Mhz 时钟,很多PLL 都实现不了 1Mhz 的时钟分频,这个就是 PLL 本身特性限制的**。

另外一种方法是使用 Verilog 代码进行分频器电路的设计

偶数分频:计数器 eg.50MHz --> 25MHz

奇数分频:

二、进阶操作

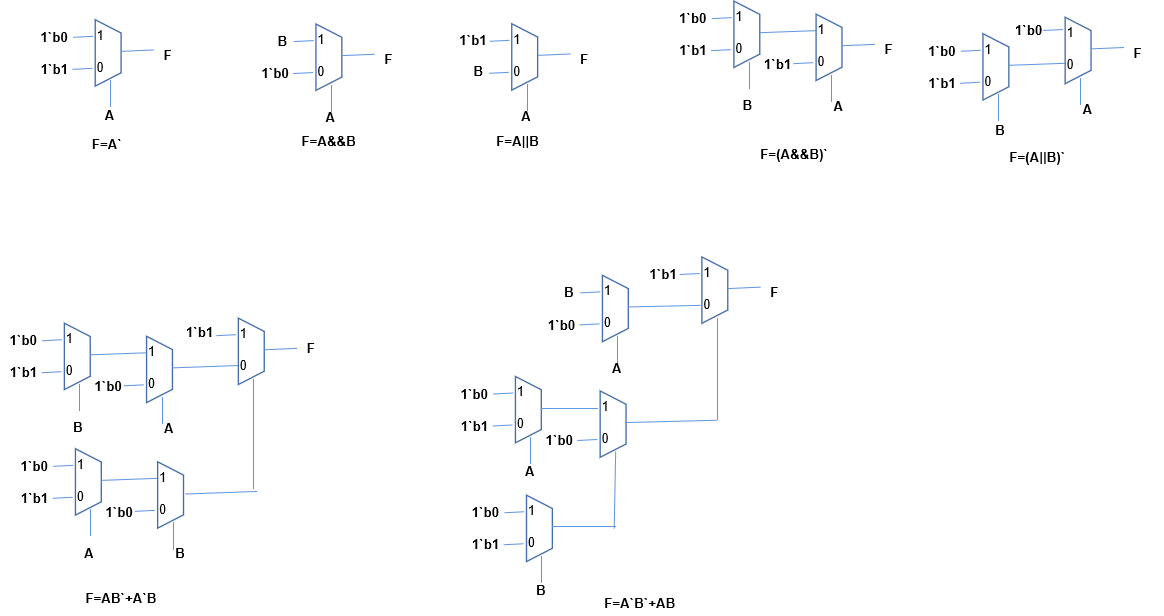

1. 使用MUX构建逻辑门

https://blog.csdn.net/vivid117/article/details/100747939

用二输入与非门、或非门搭建其他数字电路(比如数据选择器MUX)等

MUX实现逻辑功能(反相器/与门/或门/与非门/或非门/异或门/同或门)-CSDN博客

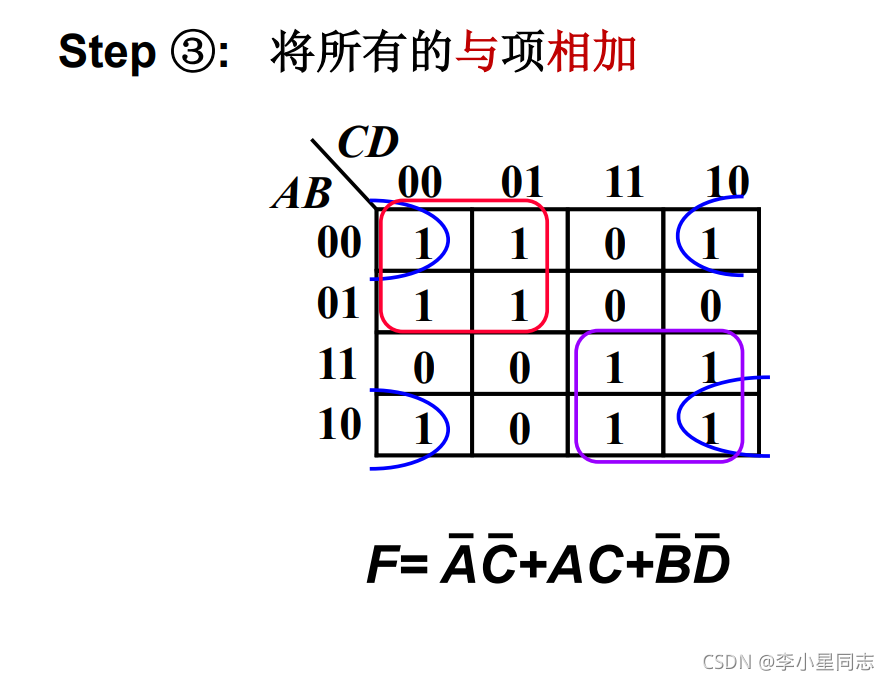

2. 卡诺图化简

**分类 : **

最简与或式(AND-OR)

最简或与式(OR-AND)

基于卡诺图的逻辑运算:

无关项合并:

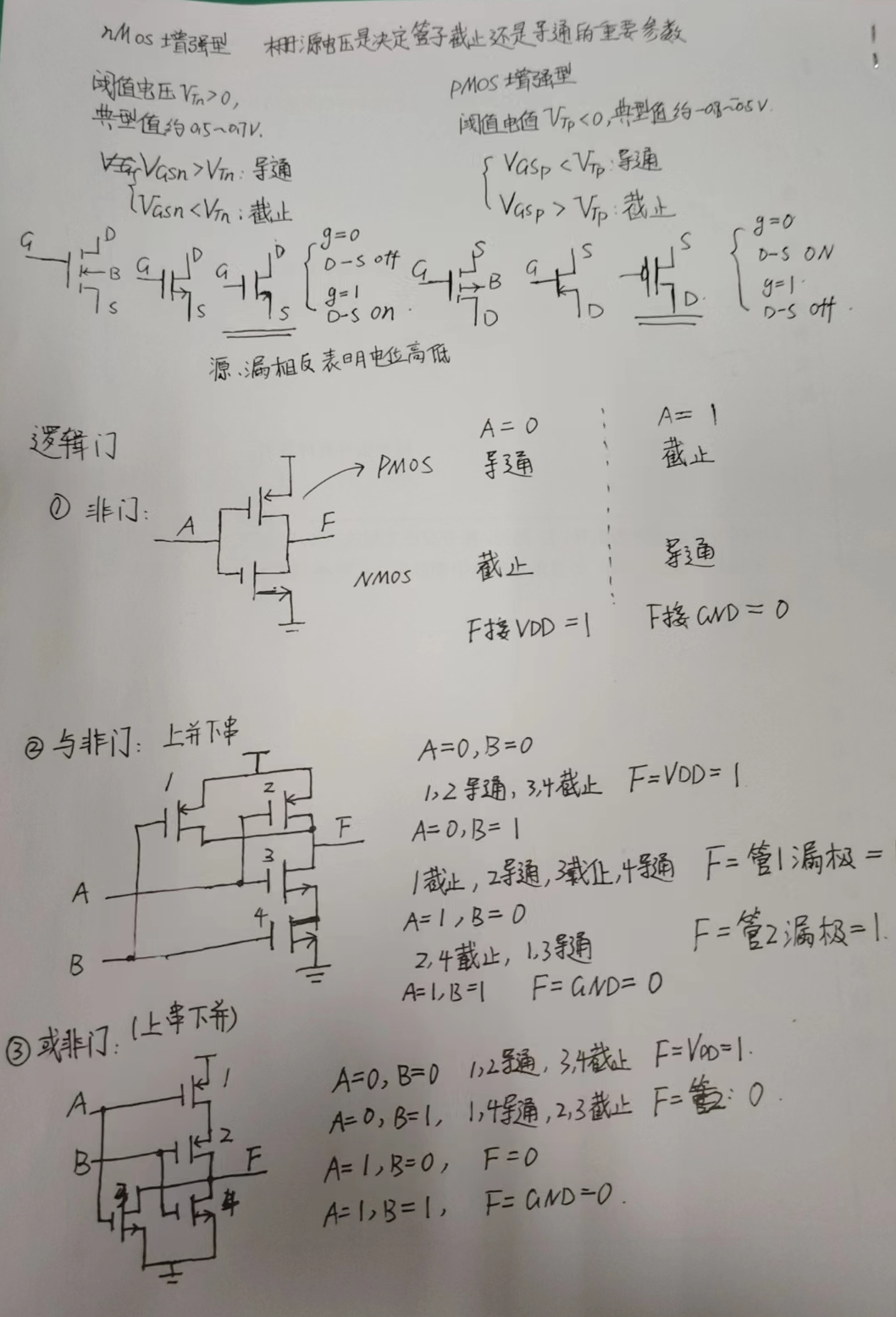

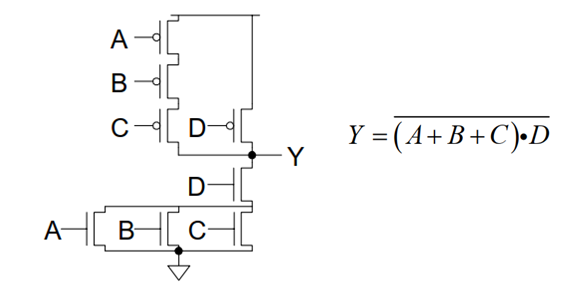

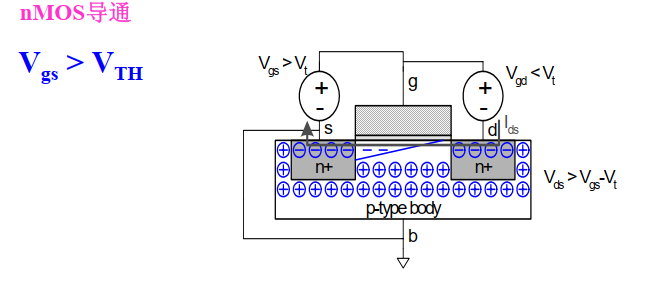

3. 使用CMOS-逻辑门

https://www.nowcoder.com/discuss/353159602411872256

3.1 非、或非、与非门

在文献中,为了画图的简便,NMOS和PMOS分别简化如下:

没有反转层生成的器件称为增强型MOS管,还有一种是耗尽型MOS,对于耗尽型MOS,中间竖线是相连的

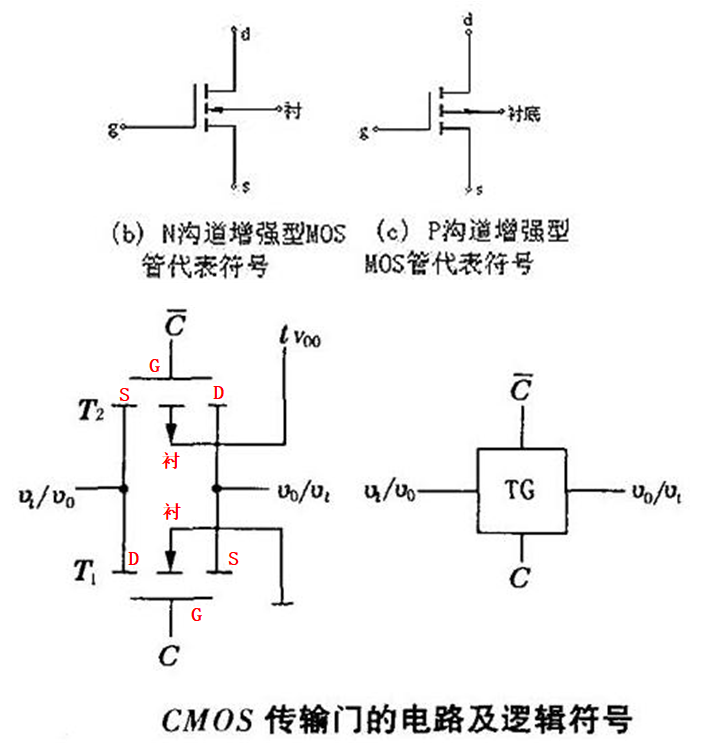

3.2 CMOS传输门

https://www.cnblogs.com/xzc943/p/13381440.html

https://mbb.eet-china.com/tech/t5/86604.html

传输门(TG)就是一种传输模拟信号的模拟开关。CMOS传输门由一个P沟道和一个N沟道增强型MOSFET并联而成

- C端接低电压-5V时TN的栅压即为-5V,vI取-5V到+5V范围内的任意值时,TN不导通;同时、TP的栅压为+5V,TP亦不导通。即 当 C端接低电压时,开关是断开的

- C端接高电压+5V。此时TN的栅压为+5V,vI在-5V到+3V的范围内,TN导通。同时TP的棚压为-5V,vI在-3V到+5V的范围内TP将导通。

- 当vI在-3V到+3V的范围内,TN和TP两管均导通;一管导通的程度愈深,另一管的导通程度则相应地减小

- 当一管的导通电阻减小,则另一管的导通电阻就增加。由于两管系并联运行,可近似地认为开关的导通电阻近似为一常数。

- 在正常工作时,模拟开关的导通电阻值约为数百欧,当它与输入阻抗为兆欧级的运放串接时,可以忽略不计。

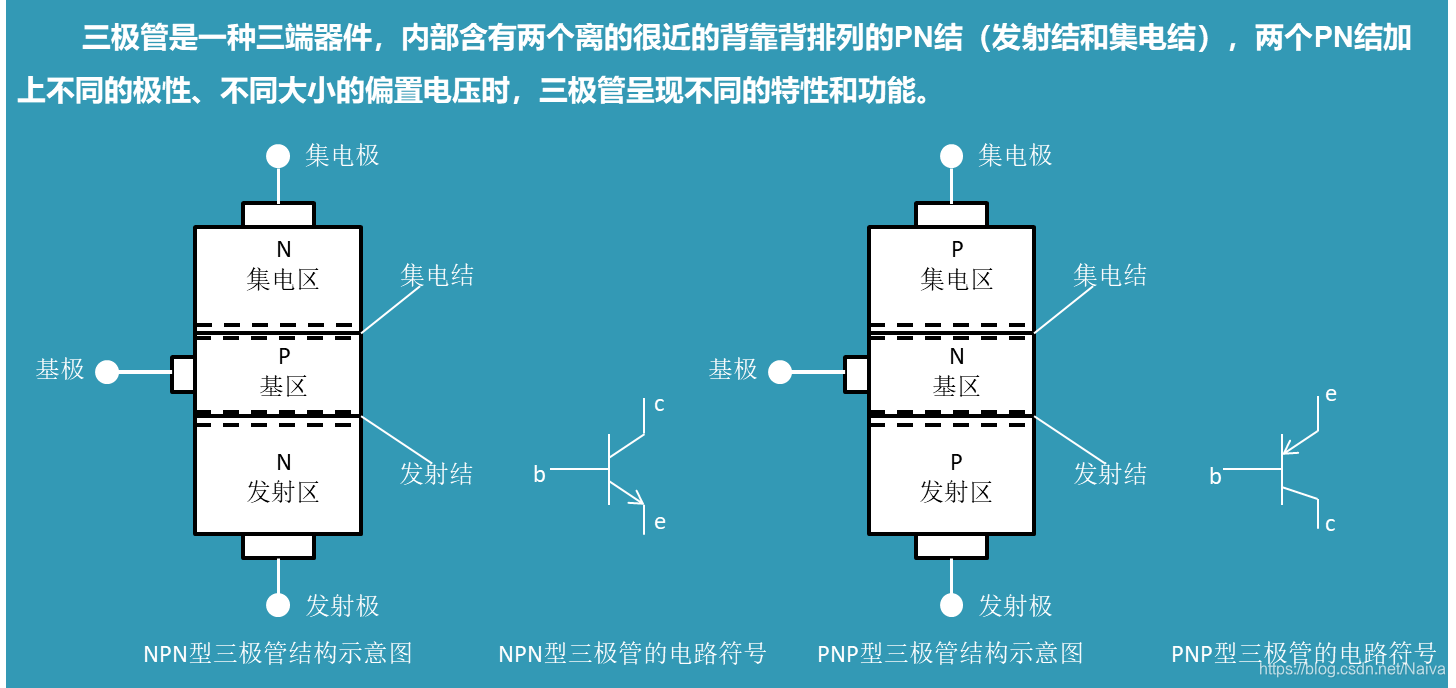

4. TTL电路(需进一步看看)

晶体管构成的门电路,被称为TTL门电路

https://www.cnblogs.com/kevinnote/p/10729893.html

5. 运算放大器电路大全

https://wuhongyi.cn/HardwareNote/Preamplifier/OperationalAmplifier.html

详见其 “参考文档)

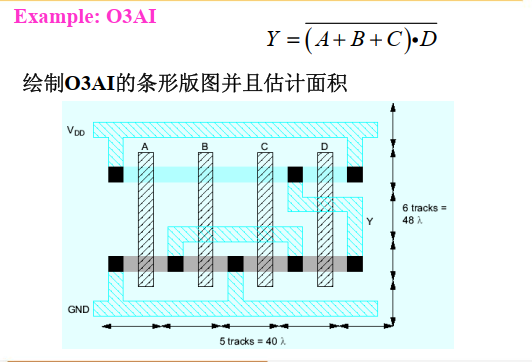

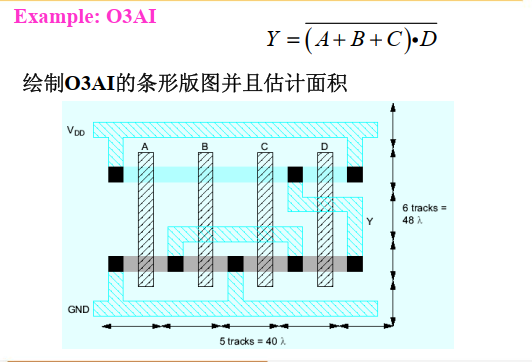

6.版图逻辑电路识别

7. OC、OD门与线与逻辑

https://cloud.tencent.com/developer/article/2163645

https://bbs.huaweicloud.com/blogs/378008

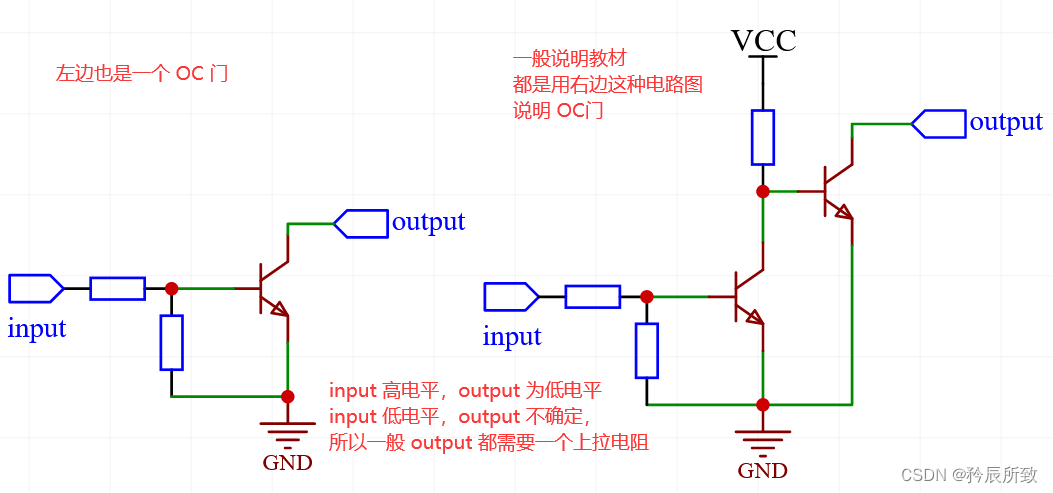

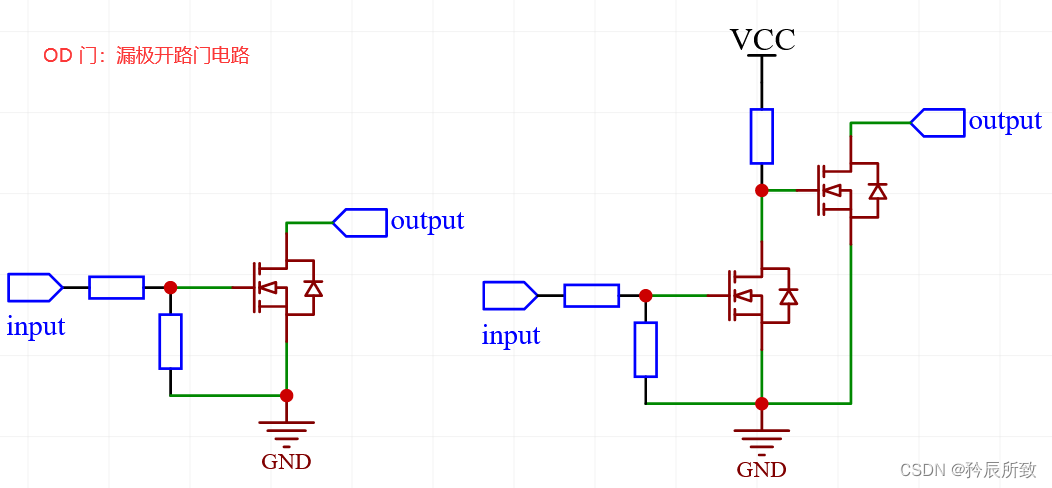

7.1 OC,OD门

OC 门input 为高电平的时候,output 实际输出不是 0V, 因为三极管存在饱和压降,一般小功率三极管大概在0.2~ 0.3V,所以output 其实为 0.3V左右。

OD 门input 为高电平的时候,output 几乎等于 0V,因为 MOS管的导通阻抗很低。

OC/OD 门电路不具备输出高电平的能力,所以在一般应用中,是需要外接上拉电阻的。

- 上拉电阻过小,会更加功耗,甚至可能烧坏 OC/OD 门。其实就是影响了回路中的电流大小,上拉电阻过小,回路电流就越大,电流越大,功耗越大,甚至超过 三极管或者 MOS 管的最大电流,烧坏管子。

7.1 线与逻辑

I2C 总线就是OC/OD门,也是因为这种 IO 的高阻态输出和线与逻辑才能让 I2C 总线能够有一个master,多个slave

https://blog.csdn.net/dongdongnihao_/article/details/80966323

图中电路,使用反相器作为输出缓冲电路

当输出为1,即或非门结果为低电平,则有导通,截止

当输出为0,即或非门结果为高电平,则有截止,导通

这样从G1的TP1端到G2的TN2端将形成一低阻通路,从而产生很大的电流,很有可能导致器件的损毁。

OD门:当两个与非门的输出全为1时,输出为1;只要其中一个输出为0,则输出为0,所以该电路符合与逻辑功能,即L=(AB)'(CD)'

8. 三极管共射、共集、共基分析

https://blog.csdn.net/zhangfan406/article/details/81974276

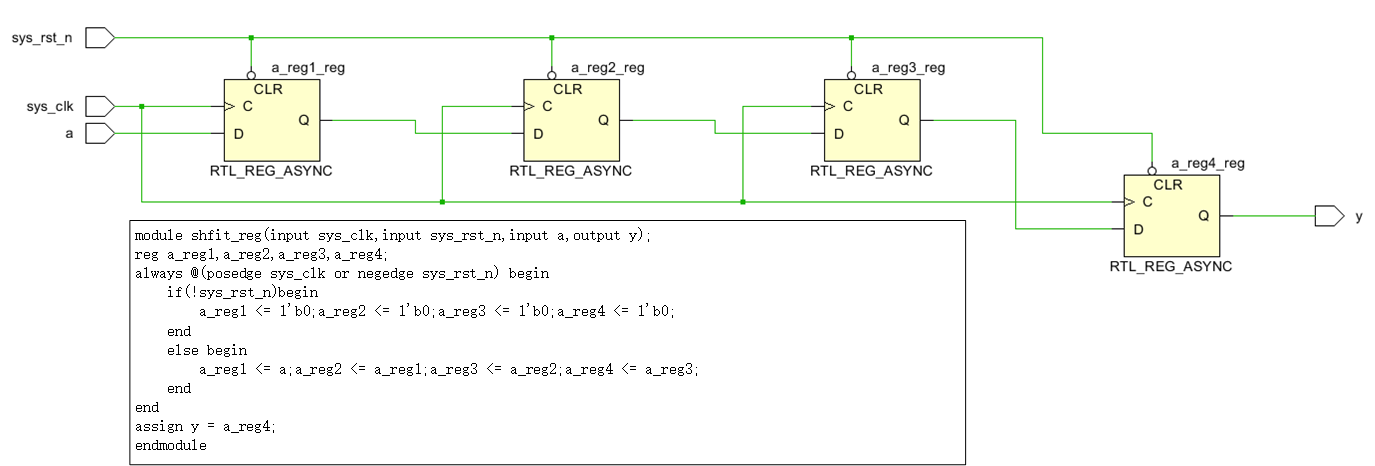

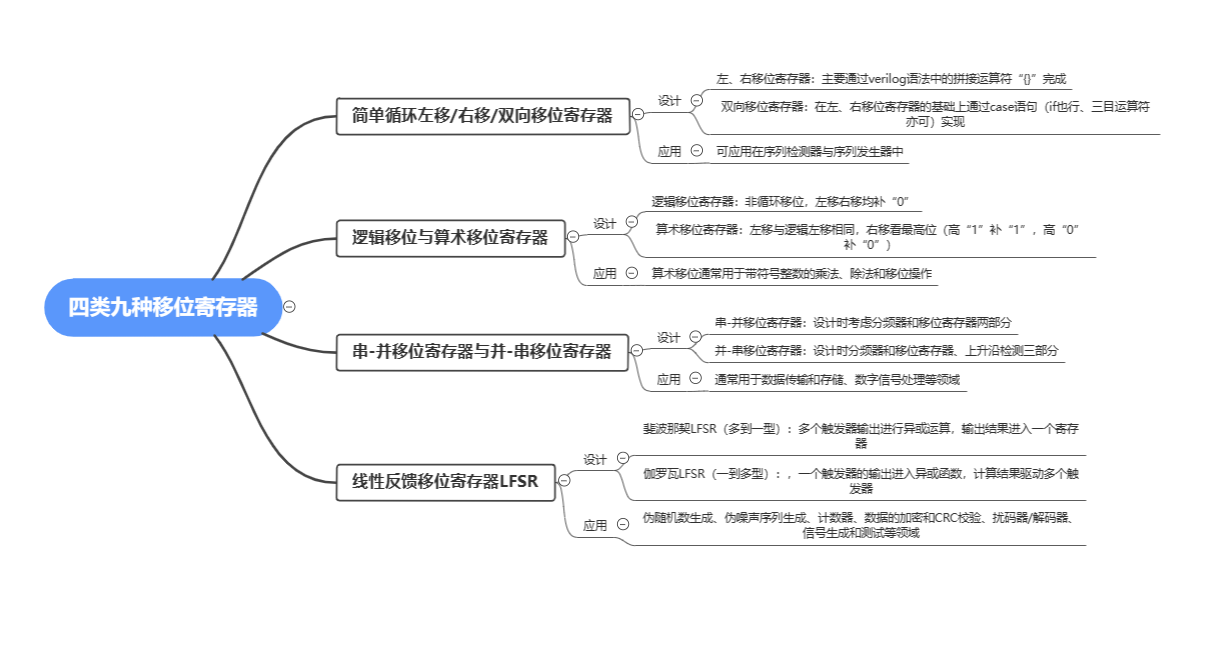

三、移位寄存器

1.移位寄存器原理与设计

原文链接:https://cloud.tencent.com/developer/article/2287337

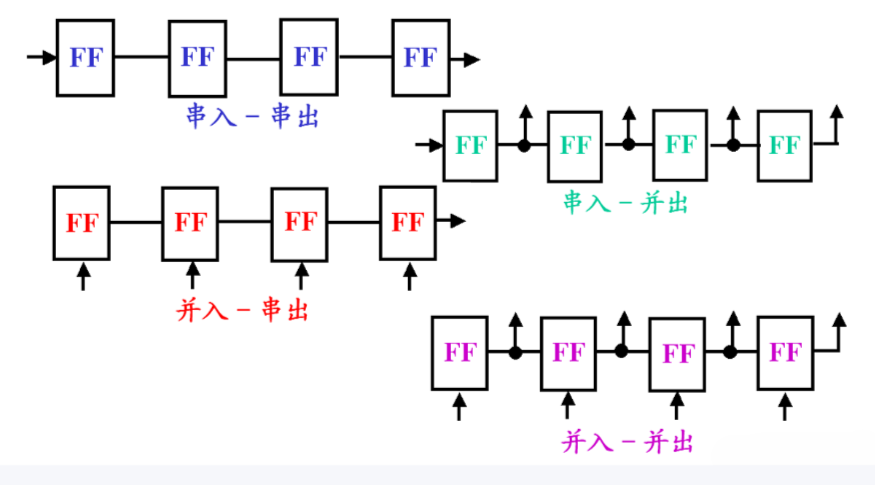

移位寄存器有哪些分类呢?

- 按移位方向分类:①单向移位寄存器(包括左移、右移)②双向移位寄存器

- 按循环方式分类:①循环移位寄存器②非循环移位寄存器

- 按部位的不同分类:①逻辑移位寄存器②算术移位寄存器

- 按输入输出方式分类:①串入串出②串入并出③并入串出④并入并出

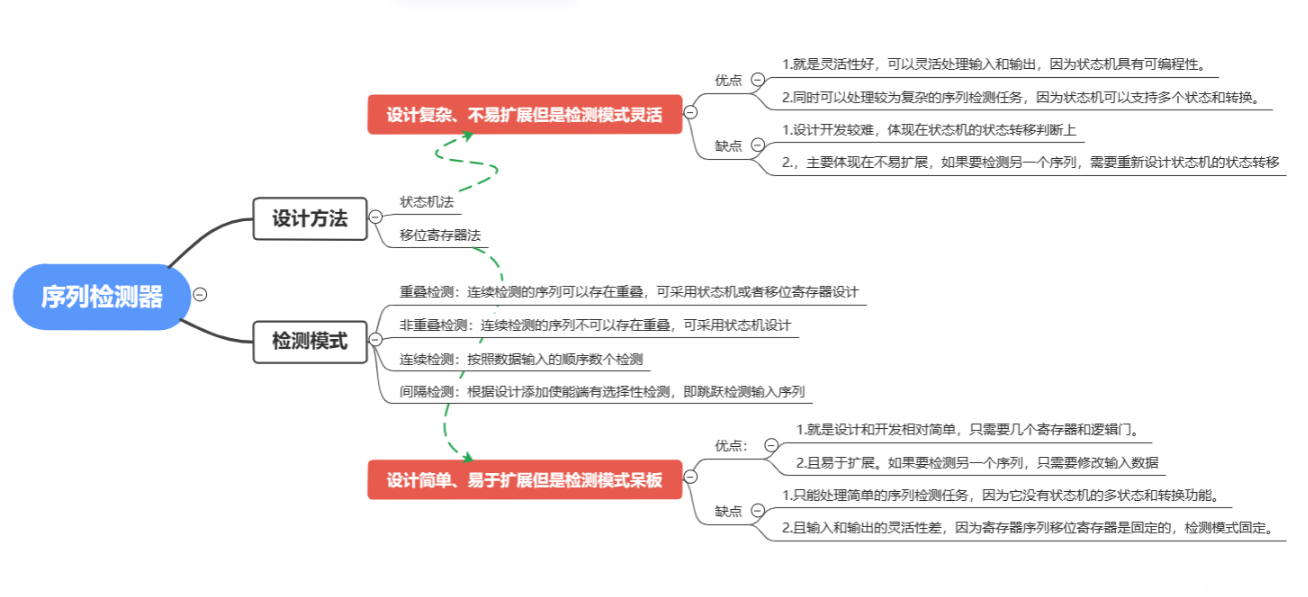

2.序列检测器

https://cloud.tencent.com/developer/article/2284746

序列检测器(Sequence Detector)是指一种特殊类型的电路,用于寻找输入信号中一定模式的子序列。

序列检测电路可以用于检测输入信号序列中是否存在特定的模式和序列,以及判断实际输出和理论输出是否存在差异。序列检测器是确保数字系统的正确运行不可或缺的一部分!

设计方法

状态机法最重要的是明白状态机状态的转移过程:在数据输入之后判断是否匹配,若匹配则进入下一状态,不匹配则根据输入的数据具体判断进入的下一状态(也有可能保持在原来的状态)。状态机设计过程一定要注重状态的数量和状态转移以及状态转移条件,避免状态的缺失以及状态转移的不合理循环。

移位寄存器法基本原理是数据的移位和移位数据的对比:首先将对应的初始数据缓存在寄存器中作为一个数组,数据输入后置于于数组的末尾,数组其它元素左移,把最早输入的数据移出,每输入一个数据后刷新一次。然后将数组和目标序列对比,如果数组和目标序列相等,则说明出现目标序列。

检测模式

重叠检测是指在一个序列中,子序列之间会有部分重叠的情况,而重叠区域也需要进行检测,并被判定为单独的子序列。

非重叠检测则是指在一个序列中,每个子序列之间没有重叠部分,因此只需要检测每个子序列本身是否满足特定的条件即可。

间隔检测模式,处理方法是添加指示信号使能端。

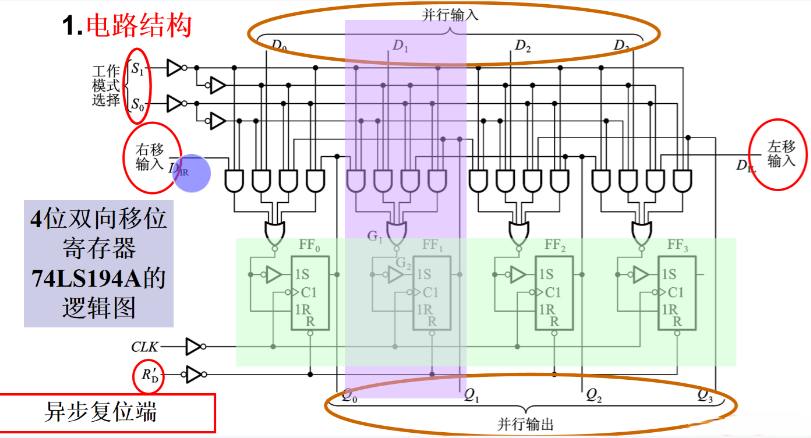

3.双向移位寄存器

目前,在定型生产的中规模移位寄存器集成电路上除了附加左、右移控制,一般还附有数据并行输入、保持、异步置零(复位)等功能。

4.串-并移位寄存器与并-串移位寄存器

数字电路中的串并转换主要设计思想来源于用面积换速度,对数据流进行管理。

实现串并转换的主要方式有双口RAM,FIFO,移位寄存器等,对于数据量较大的一般使用双口RAM或者FIFO实现,数据量较小的使用移位寄存器实现。

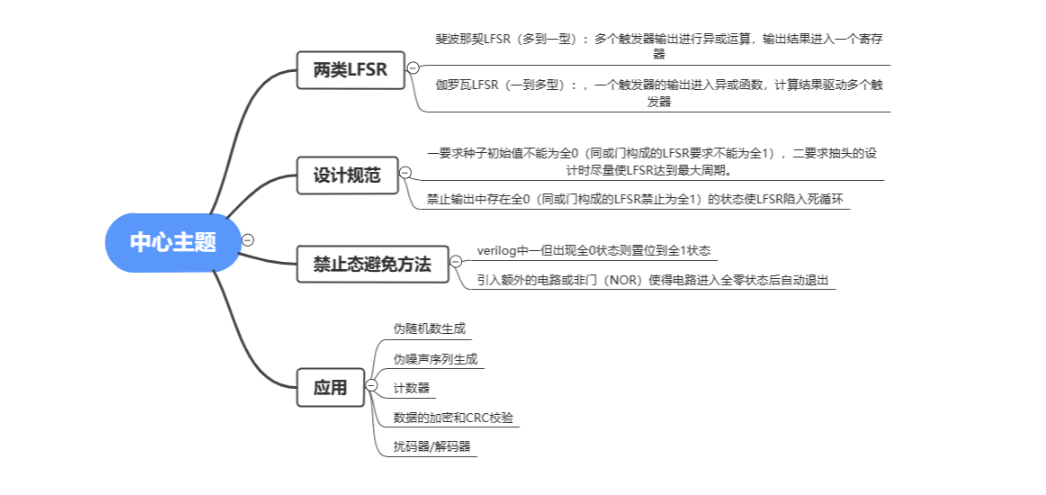

5.线性反馈移位寄存器LFSR

https://cloud.tencent.com/developer/article/2287083?from_column=20421&from=20421

- 状态:一个LFSR当前存储的序列被称为一个状态。当LFSR向右移动一位时,左侧会被反馈函数补上一位计算后的数据,得到一个新的LFSR序列,此时LFSR就移动到了一个新状态。

- 抽头:线性反馈移位寄存器有些位参与异或,有些位不参与异或,其中参与异或的位被称为抽头。抽头会影响下一状态的比特位。LFSR的触发器编号从1开始,因此抽头的取值范围是。

- 种子:LFSR中的初值,种子必须是非零的。如果为全零的话,下一状态任意做异或也还是为0,则线性反馈移位寄存器的输是无效的。

- 级数:LFSR中的寄存器个数称为LFSR的级数,例如由四个触发器组成的的LFSR的级数为4;

- 周期:LFSR所产生的伪随机序列所能遍布不循环不重复的最大数目,对于级数为4的LFSR的最大周期为 。不是所有的LFSR都能达到个周期,这与抽头的设计相关;

- 特征多项式:特征多项式表示的是抽头系数,3bit的抽头为【3,2】会产生7个状态(多项式对应为:x3+x2+1 ),抽头的设计关系到LFSR的最大周期,一般要使LFSR得到最大周期 。

反馈多项式为

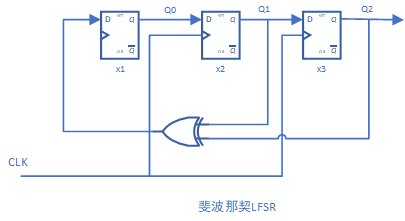

斐波那契LFSR:抽头序列对应bit位置的多个寄存器的输出异或后驱动一个寄存器输入。

即:的输入为和的输出异或后的结果

always @(posedge clk or rst_n) begin

if (!rst_n) begin

q <= 3'b111; //种子值为111

end

else begin

q <= {q[1],q[0],q[1]^q[2]}; //根据三级斐波那契LFSR电路拼接输出

end

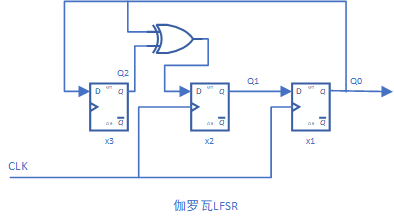

end伽罗瓦LFSR:最后一个寄存器的输出通过与抽头序列对应位置寄存器前一级寄存器的输出异或后驱动多个抽头序列对应位置的寄存器。

即:触发器x1 的输入通常来源于触发器x2的输出,x3(最高项)的输入通常来自于x1的输出,此多项式中剩余触发器的输入是x1 ,其是本机输出与前级输出异或的结果,x2 的输入由x1的输出与x3 的输出通过异或运算得到。

//时序逻辑LFSR移位模块

always @(posedge clk or rst_n) begin

if (!rst_n) begin

q <= 3'b111; //种子值为111

end

else begin

q <= {q[0],q[2]^q[0],q[1]}; //根据三级伽罗瓦LFSR电路拼接输出

end

endLFSR计数器具有速度快,消耗逻辑门少的特点。伽罗瓦LFSR具有更高的速度,因为两个触发器之间只有一个异或门。斐波那契LFSR在首尾两个寄存器之间有多个异或门,组合逻辑延时更大,因为为了满足建立保持时间的要求,其频率更小(周期更大),速度更慢。

附:遇到的问题

1.逻辑门电路与竞争冒险

竞争:当一个逻辑门的两个输入端的信号同时向相反方向变化,而变化的时间有差异的现象

冒险:两个输入端的信号取值的变化方向是相反时,如门电路输出端的逻辑表达式简化成两个互补信号相乘或者相加, 由竞争而可能产生输出干扰脉冲的现象;

当 A=B=1,由于B先经过反相器,相对于A的信号会滞后,可能导致与门最后的输出结果 会出现干扰脉冲