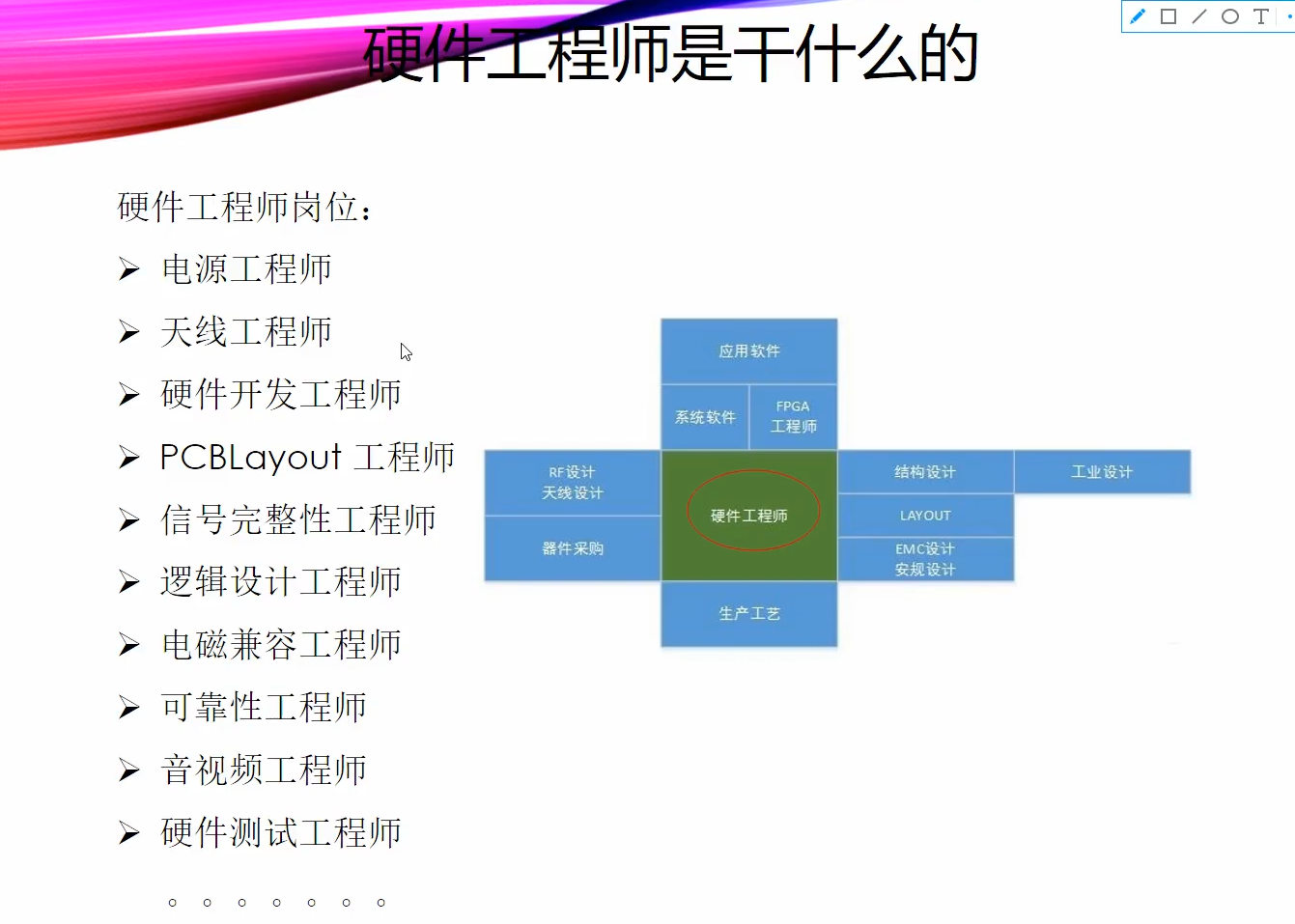

04.硬件概念

04.硬件概念

一下内容来源于:

[参阅-2] (https://www.bilibili.com/video/BV1Hm4y1n7Aq/?share_source=copy_web&vd_source=336599b4738408be4a5fb627587ab14e)

1 流程

- 需求分析

- 原理图设计

- 原理图包含:

- 封面

- 目录

- 系统框图

- 原理图

- changelist

- 原理图包含:

- layout/打板装配

- 硬件测试

- 运用焊接设备、万用表、示波器、逻辑分析仪调测

- 常用标准电路的设计:Π形滤波电路、高速信号传输线的匹配电路等

- 系统测试

- 故障定位、文档撰写

- 生产

过程中:

- 软件和脚本编写能力

- 常见硬件知识,包括电源、时钟、常见高速接口、复杂小系统(多核CPU,SOC、DSP+DDR+FLASH)

- 对信号完整性深入理解

- 熟悉EMC、可靠性、DFM设计

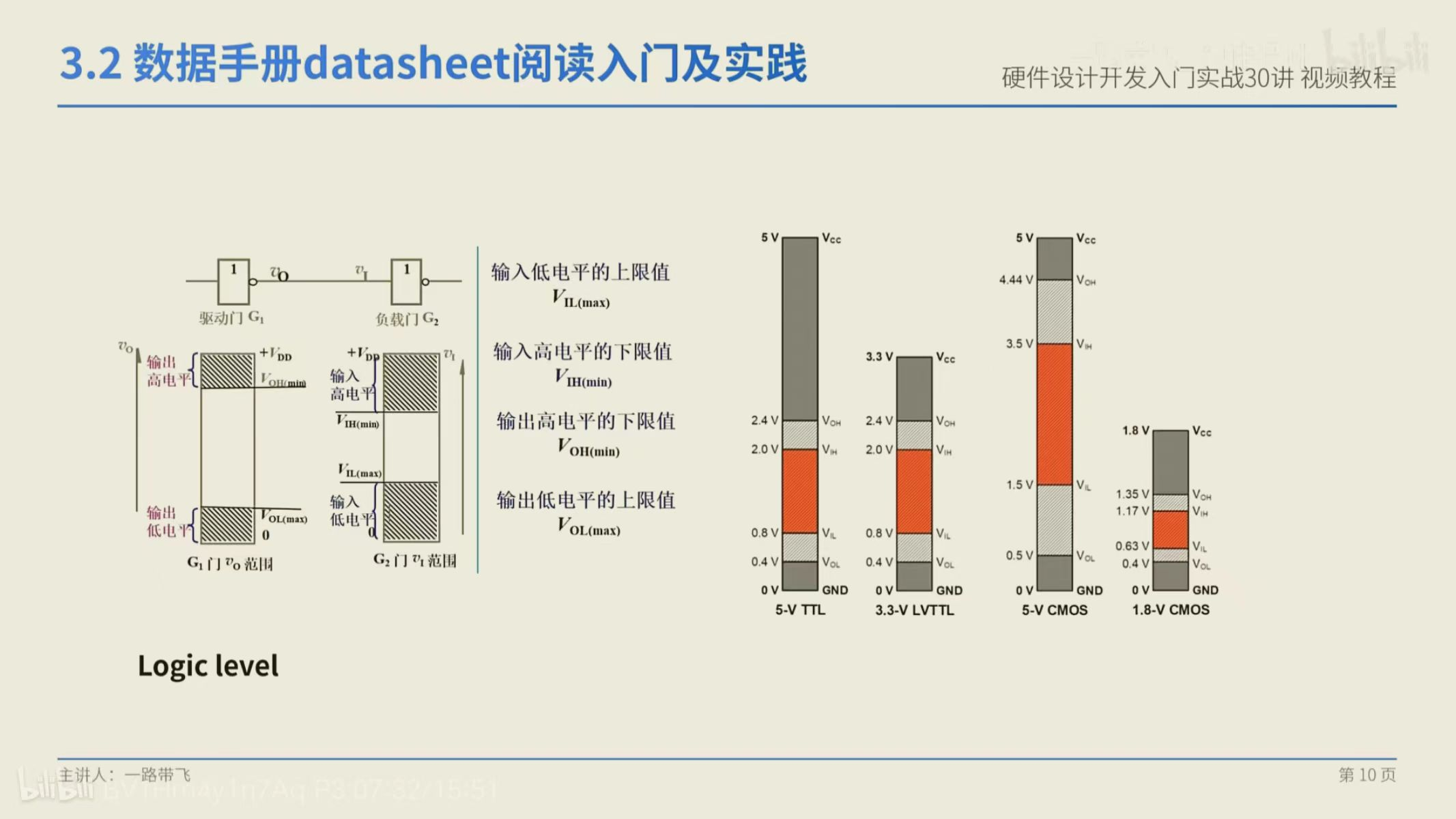

2 关于数据手册的阅读

注意点:明确目录、快速检索、专有名词及note注释说明,使用最新的手册。

手册的内容;

第一页:Feature,Applications,Description和Block Diagram

Pin Configuration and Functions 芯片的引脚及类型

Absolute Maximum Ratings 绝对值和建议值(器件的工作状态)

Electrical Characteristics 电气特性值(注意其标注的测试条件)

Logic level

logic_level 建立时间与保持时间

Register Map 寄存器表(地址及对应值的配置,写代码,debug时使用)

Typical Application 典型应用 包含一些电路的范例

Layout guideline 布局布线参考(PCB设计)

PACKAGE 封装及symbol设计参考

3 关于最小系统

以单片机为例,是指单片机可正常执行程序的最简工作环境。

- 电源

- 复位 如低电平复位,上电瞬间,利用电容充电,信号出短暂的低电平,其持续时间由电阻电容电路决定

- 时钟 系统的心脏

- 调试接口

- 启动

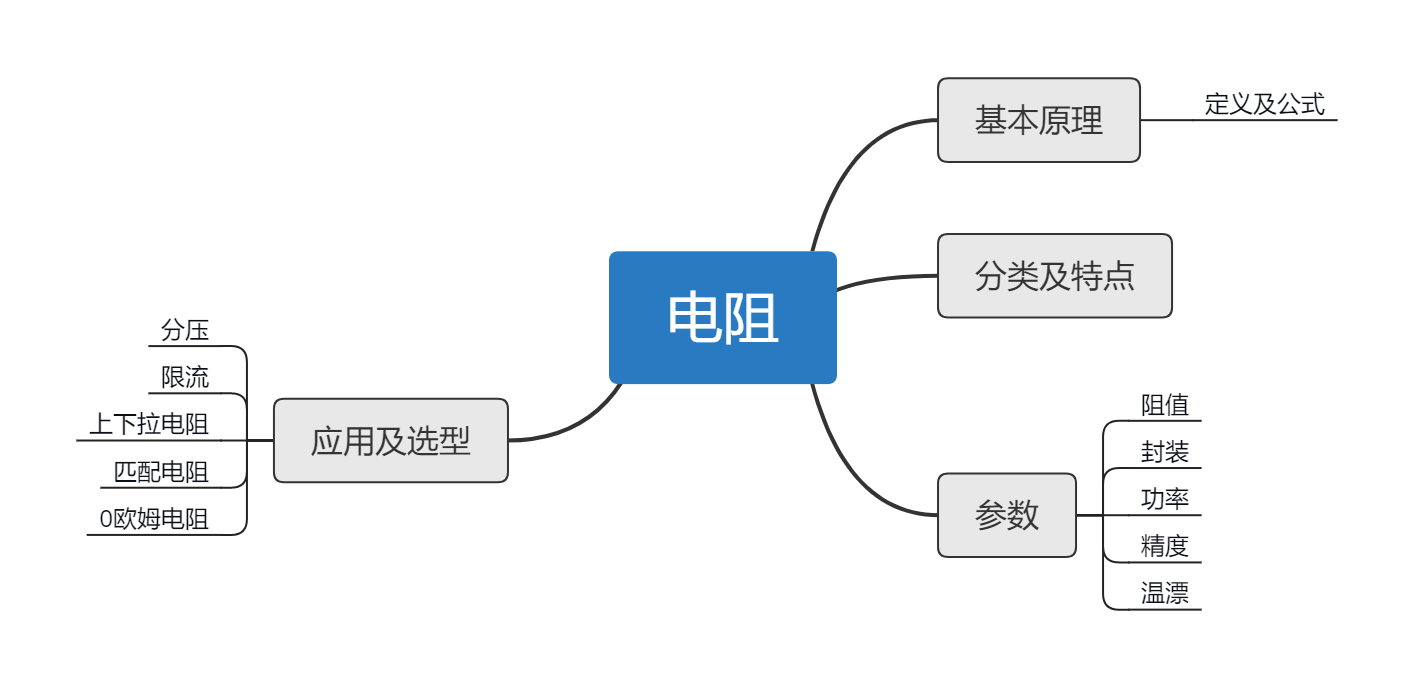

4 电阻

式1为定义式,式2中表明电阻率,表明电阻长度,表示电阻的横截面积

电阻的串并联、功率,电能

分类

- 功能

- 材料

- 形状

应用

分压:串联电阻分压、负反馈放大器

上下拉电阻:将状态不确定的信号线通过一个电阻将其箝位至高电平(上拉)或低电平(下拉)。

对于非集电极(或漏极)开路输出型电路(如普通门电路,其提升电流和电压的能力是有限的,上拉和下拉电阻主要功能是为集电极开路输出型电路提供输出电流通道。上拉是对器件注入电流,下拉是输出电流;强弱只是上拉或下拉电阻的阻值不同)。

高有效的使能控制信号(下拉电阻以保持无效状态),低有效的复位控制信号(上拉电阻以保持无效状态)

匹配电阻:高速信号设计中的阻抗匹配(传输线)

0欧电阻:跨线电阻器

- 跳线

- 预留

- 增加测试点

5 电容(未完)

6 三极管、场效应管、MOS管

6.0 基础概念(核心)

从原理的视角,一文彻底区分MOS MOSFET NMOS PMOS CMOS

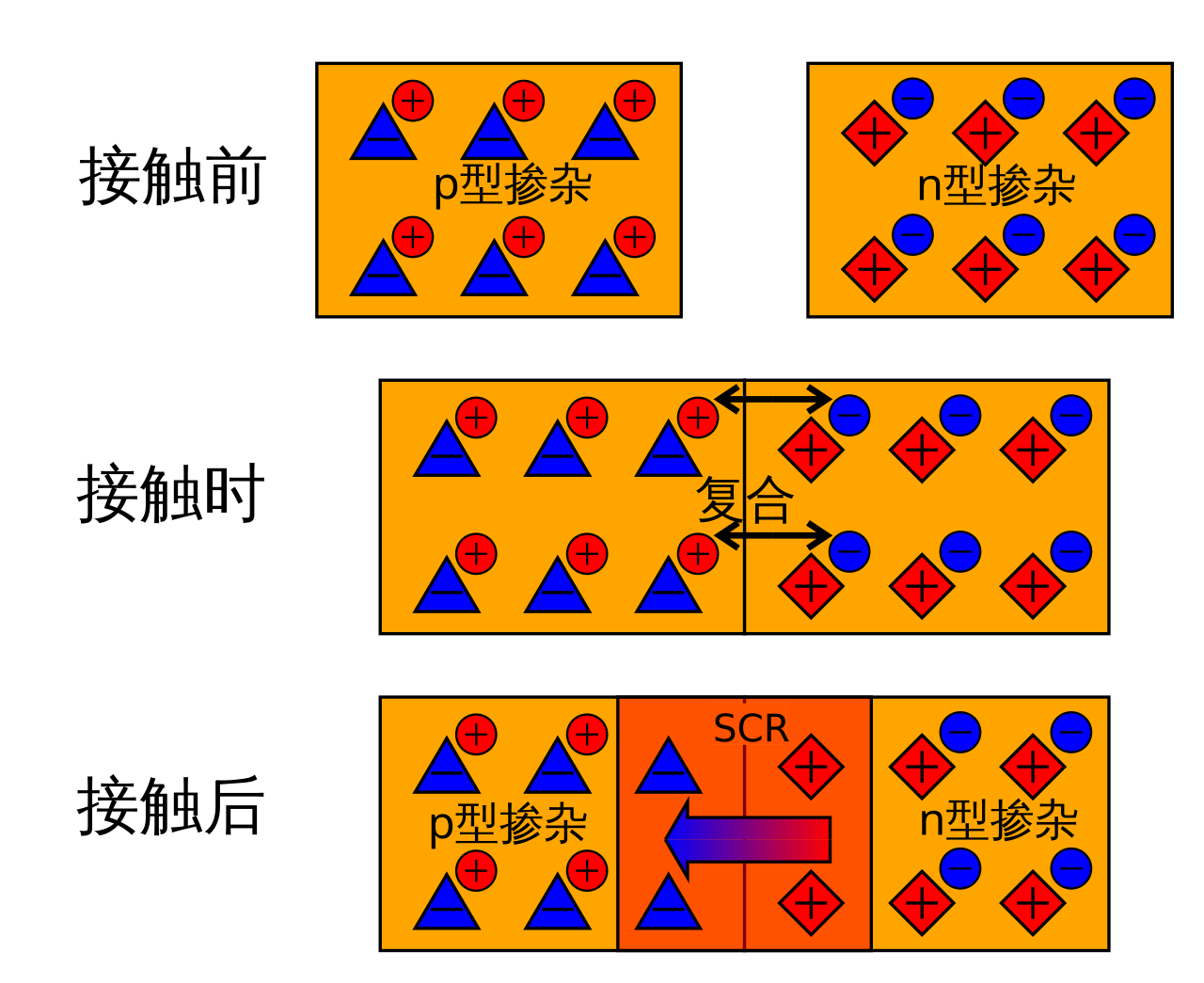

金属-氧化物-半导体 MOS

PN结效应

N型半导体:含自由电子浓度较高的半导体

载流子经过扩散的过程后,扩散的自由电子和空穴相互结合,使得原有的N型半导体的自由电子浓度减少,同时原有P型半导体的空穴浓度也减少。在两种半导体中间位置形成一个由N型半导体指向P型半导体的电场,称为“内电场”。

零偏置

正向偏置

反向偏置

NMOS

1.没有施加电场时,G极下没有产生N沟道,所以电路图中用虚线代表这一层意思。(G极为0V,没有反转层生成的器件称为增强型MOS管,还有一种是耗尽型MOS,对于耗尽型MOS,中间竖线是相连的。)

2.箭头的意思代表衬底的PN结效应,P型衬底(NMOS)在G极产生电场下,靠近G极为电子区、远离端为空穴区,所以电场下生产的PN效应指向G极

3.图中的二极管是衬底与D之间体二极管,上文中也提到了,如果衬底接高电平,此时二极管直接导通,失去了MOS管控制的作用。大家此时应该立刻想到,如果NMOS的S极接了高电压,D接了低电压,MOS管直接导通!

在文献中,为了画图的简便,NMOS和PMOS分别简化如下:

三极管、场效应管和MOS管三者的工作原理:https://blog.csdn.net/m0_51390088/article/details/124323094

6.1 三极管

https://blog.csdn.net/Naiva/article/details/90045788

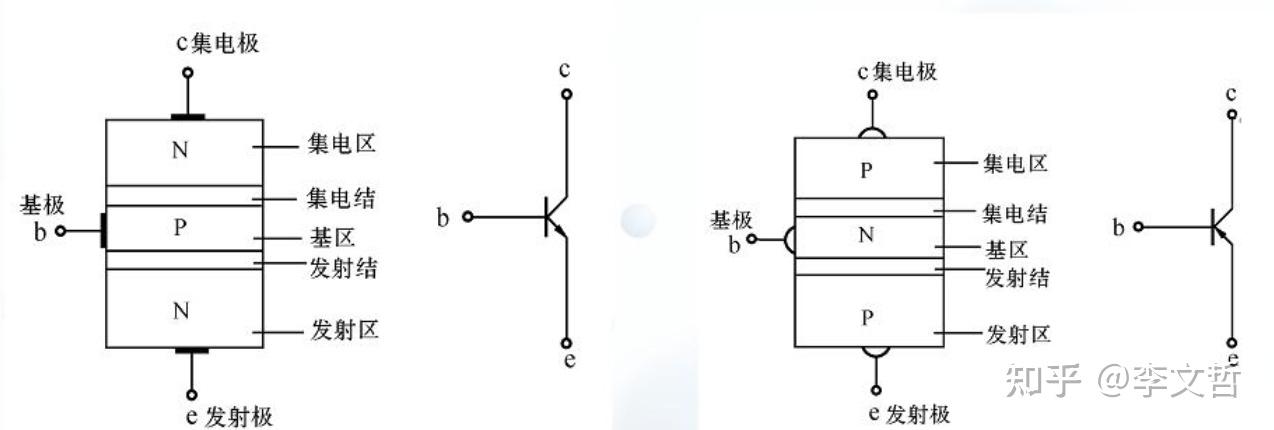

- NPN型:电流方向由基极和集电极流向发射极,发射极处的箭头指离基极。

- PNP型:电流方向由发射极流向集电极和基极,发射极处的箭头指向基极。

三极管导通:

U2大于一定的数值(一般是0.7V),则发射结正偏,基极注入小电流,会吸引发射极电子往集电极流动,三极管导通。

电流放大:

三极管器件内部三个区域存在不同的掺杂浓度,其中发射级浓度远大于基极浓度,此时发射机大量电子往集电极流动,从而放大基极电流。

工作状态 :

- 截止状态 : 三极管处于关断状态,Vce约等于电源电压

- 放大状态 :三极管处于电流放大状态,0V

- 饱和状态:三极管处于完全导通状态,Vce≈0V

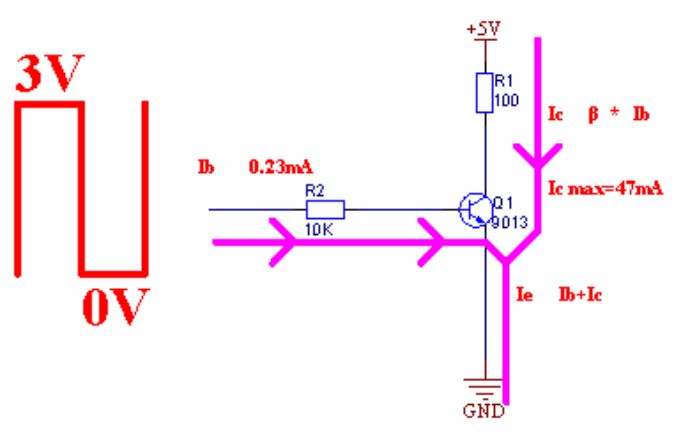

NPN-三极管放大电路(信号型三极管)

典型特征:

note : 在三极管饱和导通时,,假定(其值辉随着温度、湿度灯发生变化)

有:

三极管放大状态下会随着的增大而增大,减小而减小

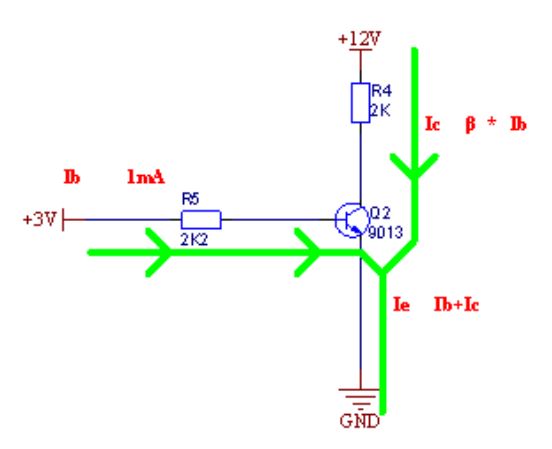

NPN-三极管饱和状态(信号型三极管)

典型特征:

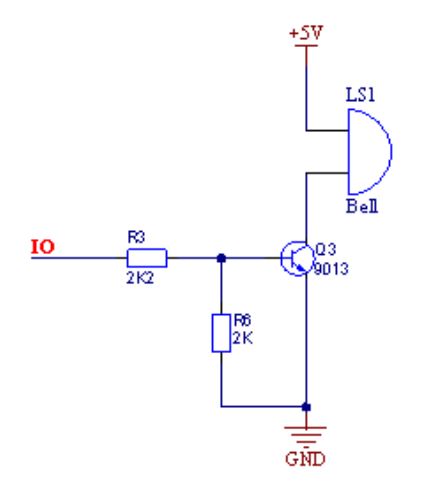

NPN 开关管实际应用电路

当三极管都是和单片机IO口相连做开关控制使用,假设此时单片机IO口出现高阻态,那么接入三极管IB的电平就是不确定的会导致三极管误导通,此时如果接有下拉电阻根据内阻分析法会给IB一个稳定的状态,不会导致三极管误触发,

下拉电阻的作用:当无输入或者输入是高阻态时,通过下拉电阻将基极迅速拉低,确保三极管处于稳定的截止状态。

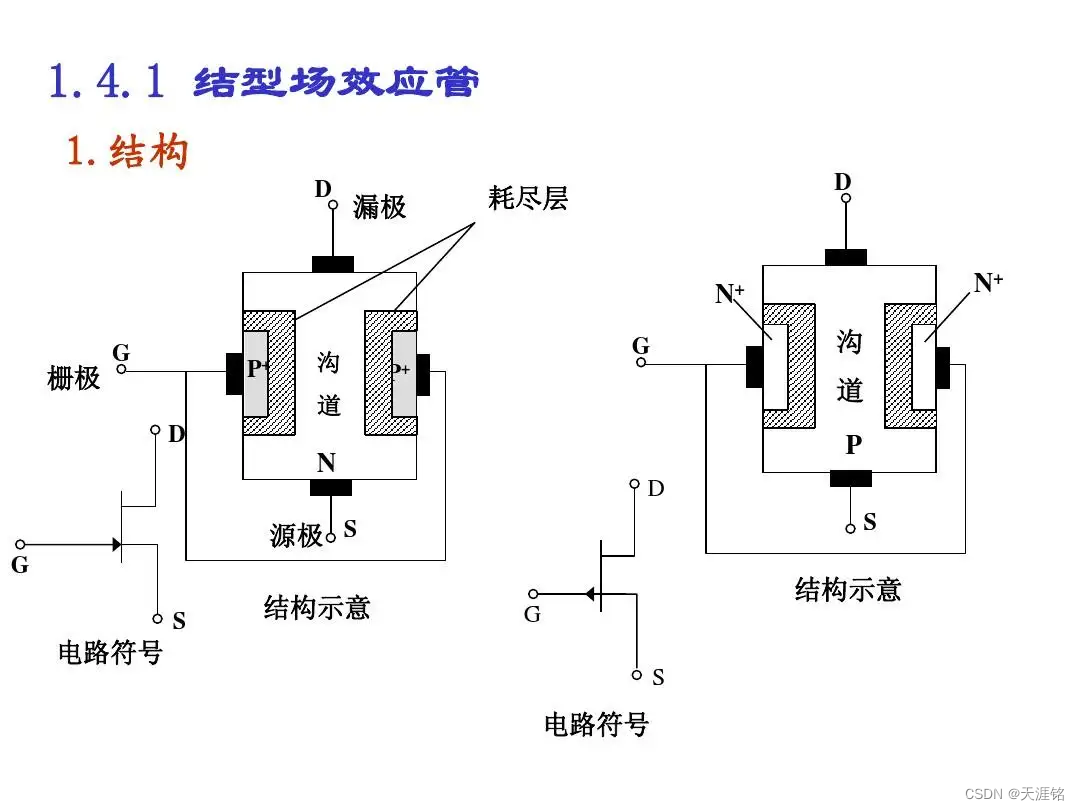

6.2 结型场效应管(JFET)

https://blog.csdn.net/STM89C56/article/details/124959048

栅极(Gate)、源极(Soure)和漏极(Drain)。场效应管分为N沟道和P沟道场效应管

内部构造:

N沟道场效应管

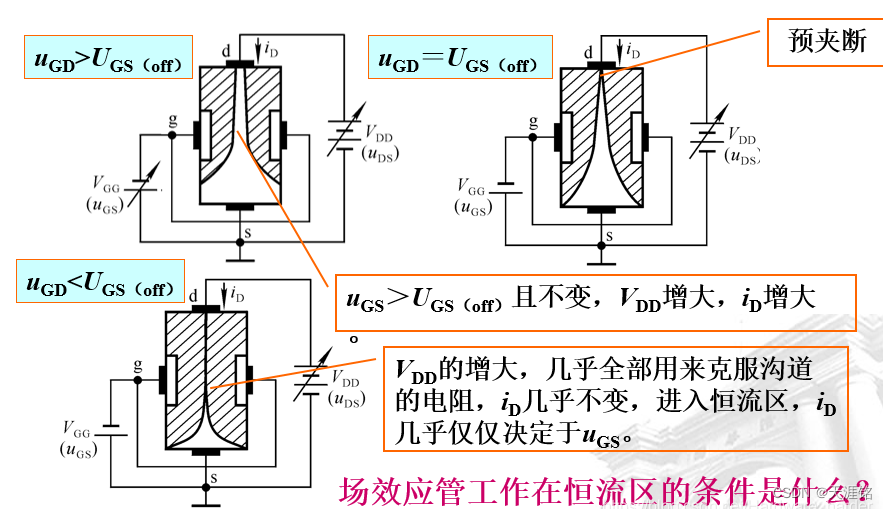

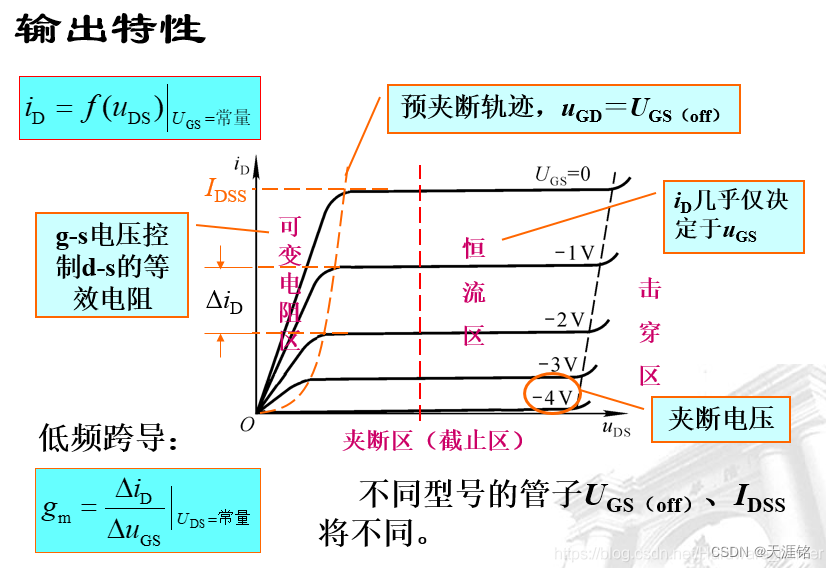

- 场效应管生而导通,如果栅极和源集之间电压为0时,源集电子往漏极走,此时漏极和源极之间的电流最大

当之间的压差大于一定的数值,放在N沟道场效应管中就是栅极电压低于源极电压一定的数值,则场效应管之间就没有贯通电场,使得漏极与源极之间没有电流

栅极能够控制场效应管的通断,而漏极电压对于沟道的控制是双向控制,无法夹断沟道,大于一定的数值,沟道就会达到一个平衡点,进入恒流区

6.3 MOS管(绝缘栅场效应管)

https://www.nowcoder.com/discuss/353159602411872256

现在主要为增强型MOS管

金属氧化物场效应晶体管(MOSFET),G(Gate,栅极),D(Drain,漏极),S(Source,源级)。场效应管分为 PMOS 和 NMOS,属于绝缘栅场效应管。

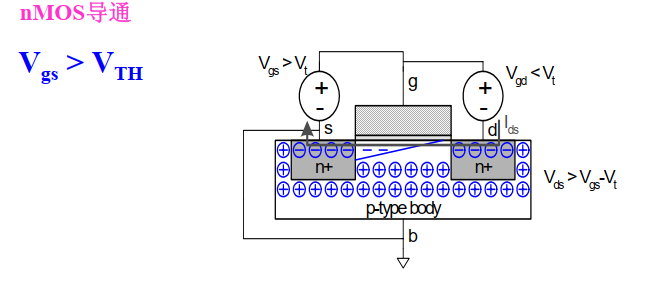

对于NMOS

,栅极和源极电压相同,在源极和漏极间施加电压,总有一个PN结反偏,MOS管不导通

在这里插入图片描述 (门槛电压,eg 0.7v)

在栅极的SIO2内部会形成电场,从而吸引P衬底的电子而排斥空穴,在N极之间形成反型层次,即导通通道

- 时,电流随的增加而增加,达到阈值后进入恒流区

6.4 CMOS

CMOS即 complementary MOSFET,互补型MOSFET,在大规模集成电路里面,NMOS和PMOS被集成在一起,通过同一个信号来控制,从而实现数字信号的逻辑NOT功能。这种结构是组成集成电路的基础单元。