04.琐碎知识

04.琐碎知识

1.fpga .ucf 文件转xdc

在FPGA设计中,.ucf文件是用户约束文件,而.xdc文件是Xilinx约束文件,它们都用于指导FPGA的实现过程,但是.ucf文件主要是针对老版本的Vivado工具,而.xdc文件则是针对新版本的约束文件。

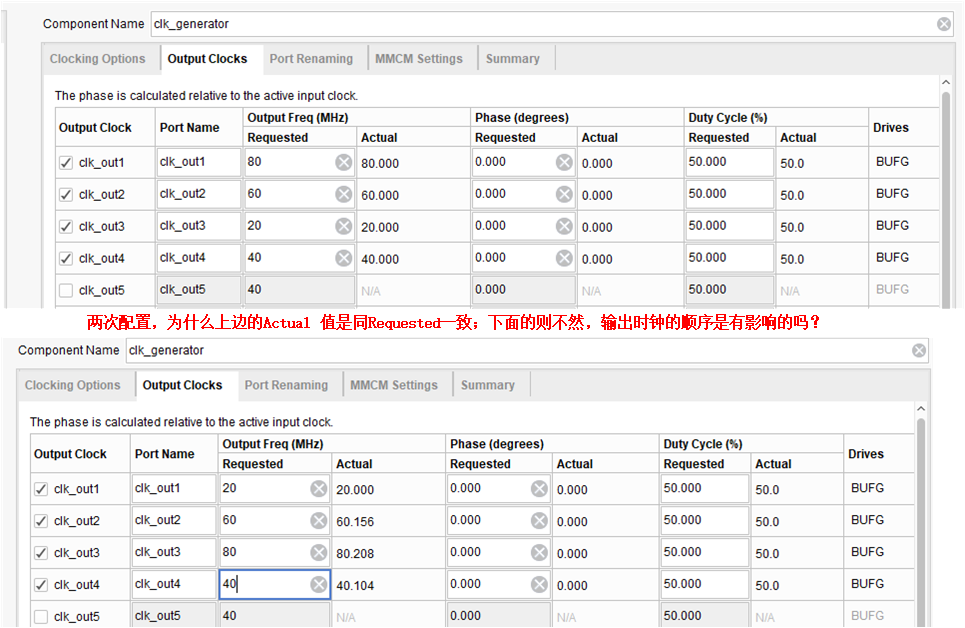

2.clock_wizard IP核配置问题

https://blog.51cto.com/u_15338162/5206365

导出CLK_OUT信号的电路的优先级是CLK_OUT1> CLKOUT2> CLKOUT3,依此类推。 因此,找到CLK_OUT1频率的解决方案具有更高的优先级。 每次输入更改时都会重新计算值。

IP手册说明:https://docs.amd.com/r/en-US/pg065-clk-wiz/Output-Clocks?tocId=sKRn19Az2NIbXIkdZQZagQ

If it is not possible to comply exactly with the requested parameter settings due to the number of available input clocks, best-attempt settings are provided. When this is the case, the clocks are ordered so that clk_out1 is the highest-priority clock and is most likely to comply with the requested timing parameters. The Wizard prompts you for frequency parameter settings before the phase and duty cycle settings.

芯片的常用封装形式:

SO、SOP、SOIC、MSOP、TSSOP、TSOP、VSSOP、SSOP、SOJ封装详解

常用芯片封装形式:https://blog.csdn.net/KeepSomething/article/details/92636424

程序跑飞:

在硬件开发中,程序跑飞(Program Runaway)是指系统受到某种干扰后,程序计数器(Program Counter, PC)的值偏离了给定的唯一变化历程,导致程序运行偏离了正常的运行路径。这种现象可能由多种因素引起,包括但不限于:

- 干扰信号直接作用到CPU上,导致CPU不能按正常状态执行程序,从而引起混乱。

- 供电电压不稳定或不在正常工作电压范围内,电源纹波大小过大。

- 晶振以及旁路电容的配置不当,如没有尽可能地靠近单片机。

- 电路中有裸露的接口,如USB IO口等,可能会因为静电传导而引起单片机复位或死机。

- 无线射频信号的干扰,如蓝牙、WiFi、GSM等无线射频信号可能会因为无线辐射干扰造成单片机死机。

- 中断处理不当,例如未响应或清除中断标志,导致程序一直进入中断,造成死机假象。

- 地址溢出,常见错误为指针操作错误,例如循环变量未控制好,导致数组下标越界,意外修改系统的寄存器造成死机。

程序跑飞后,系统可能会出现不可预测的行为,如进入死循环、死机或表现出异常行为。在软件设计中,为了防止程序跑飞,通常会采取一些防范和处理措施,如:

- 设置监视器:在程序的关键位置设置监视器(如看门狗定时器),一旦程序运行异常,监视器可以自动将程序复位或重启。

- 中断管理:确保每个开启的中断都有相应的中断服务程序,并正确处理中断返回,避免因中断处理不当导致程序跑飞。

- 内存保护:使用内存保护机制,如内存锁或其他硬件支持的功能,防止程序访问非法内存区域。

- 数据隔离:确保程序中的数据区域和代码区域分开,避免数据操作影响到代码执行。

- 指针检查:对数组和指针操作进行严格的边界检查,避免越界访问。

此外,还可以采用指令冗余、软件陷阱技术、代码优化、模块化设计等方法来增强软件的健壮性和可靠性,以减少程序跑飞的风险。

总之,程序跑飞是硬件开发中需要重点关注和防范的问题之一,需要在软件设计和硬件设计时采取一系列措施来确保系统的稳定性和可靠性。

时钟信号知识点全解析

同源时钟:只同一个时钟源衍生频率比值为2的幂次方,且初相位相同的时钟。

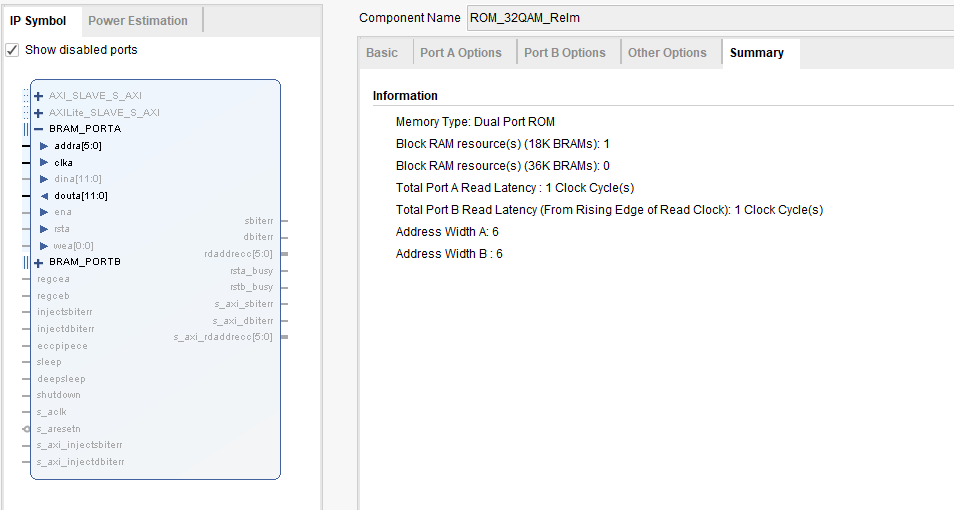

3. 输入双口ROM地址的延迟(未进一步分析)

module QAMModulator_32QAM (

input wire Clk,

input wire SRst,

input wire Start,

input wire DataValidIn,

input wire Data,

output reg ModDataOutValid,

output reg [7:0] DataNum,

output wire signed [11:0] ModDataOutRe,

output wire signed [11:0] ModDataOutIm

);

// Define the size of the LUT

reg [4:0] CurrBits = 5'd0;

reg [5:0] CurrBits_32=6'd32;

wire [5:0]CurrBits_a;

assign CurrBits_a=CurrBits+6'd32;

// 使用CurrBits_32 和CurrBits_a 会产生不同的结果

ROM_32QAM_ReIm LUT_32QAM (

.clka(Clk), // input wire clka

.addra({1'b0,CurrBits}), // input wire [5 : 0] addra 0~31 实部信号

.douta(ModDataOutRe), // output wire [11 : 0] douta

.clkb(Clk), // input wire clkb

.addrb(CurrBits_a), // input wire [5 : 0] addrb 32~63 虚部信号

.doutb(ModDataOutIm) // output wire [11 : 0] doutb

);

parameter IDLE = 0;

parameter Gen32QAM = 1;

parameter Gen32QAM_2 = 2;

reg [1:0]State = IDLE;

reg [3:0] CurrBitCount = 0;

reg [15:0] DataCount = 0;

always @(posedge Clk) begin

if (SRst) begin

State <= IDLE;

ModDataOutValid <= 0;

DataCount <= 0;

CurrBitCount <= 0;

CurrBits <= 5'd0;

CurrBits_32=6'd32;

end else begin

ModDataOutValid <= 0; // Default output valid

case (State)

IDLE: begin

DataCount <= 1;

CurrBitCount <= 0;

CurrBits <= 5'd0;

CurrBits_32=6'd32;

if (Start) begin

State <= Gen32QAM;

end

end

Gen32QAM: begin

if (DataValidIn) begin

CurrBitCount <= CurrBitCount + 1;

CurrBits <= {CurrBits[3:0], Data}; // Shift in the new bit

CurrBits_32=6'd32+{CurrBits[3:0], Data};

if (CurrBitCount == 4) begin

CurrBitCount <= 0;

State<=Gen32QAM_2;

end

end

end

Gen32QAM_2:begin

if (DataValidIn) begin

CurrBitCount <= CurrBitCount + 1;

CurrBits <= {CurrBits[3:0], Data}; // Shift in the new bit

CurrBits_32=6'd32+{CurrBits[3:0], Data};

end

ModDataOutValid <= 1;

DataCount <= DataCount + 1;

if (DataCount == 16'h1000) begin // 4096 in decimal

State <= IDLE;

end

else

State <= Gen32QAM;

end

default: begin

State <= IDLE;

end

endcase

end

end

endmodule

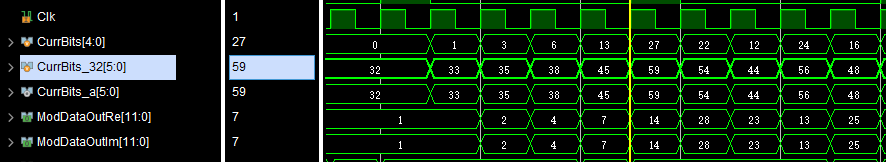

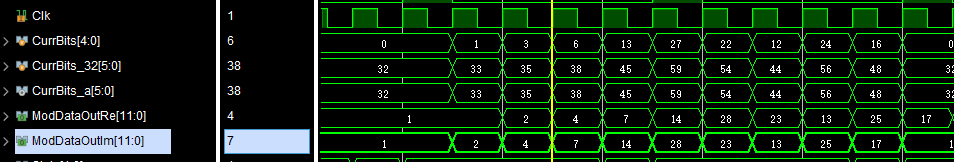

对于上述代码:

若是 双口ROM的

addrb使用CurrBits_a,则ROM的输出结果延迟于地址一个clock时钟,符合ROM-ip的配置(ROM ip中存储为 1,2,...,32,1,2,...,32)

若是

addrb使用CurrBits_32,则ROM的输出结果和地址变化同周期,出现错误错误:对于ROM的B端口,输出数据和地址表现为同一个时钟

Clk上升沿变化,这不符合逻辑

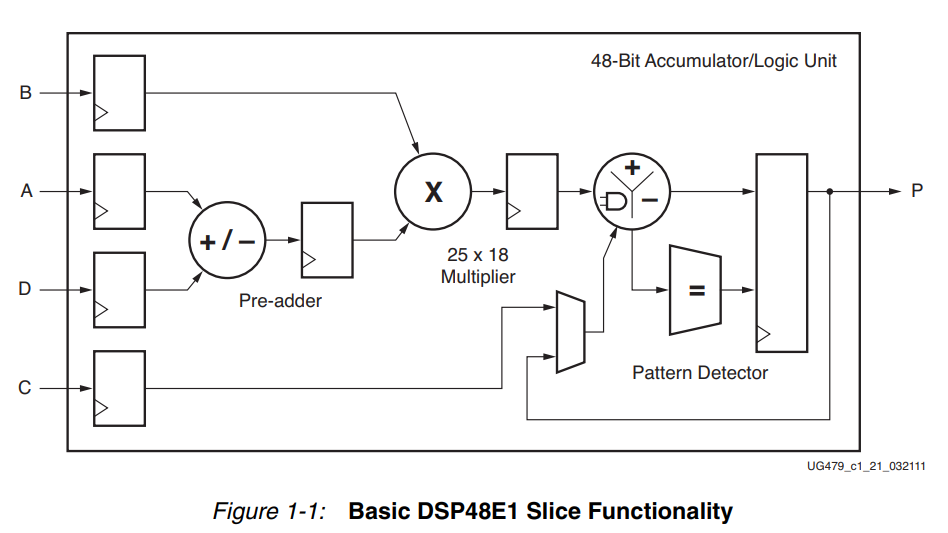

4. DSP48E1

DSP48E1:https://zhuanlan.zhihu.com/p/158887086

https://docs.amd.com/v/u/en-US/ug479_7Series_DSP48E1

在实际的编码过程中,合理充分的利用DSP48E1不仅可以节约不少CLB资源,还能提高整个FPGA系统的性能。

DSP48E Example: Creating a Complex Multiplier

Efficient Implementation of Complex Multipliers on FPGAs Using DSP Slices