05.实践-Zynq7010

05.实践-Zynq7010

硬件篇

- 概念:核心板,底板,开发板

https://blog.csdn.net/irene3/article/details/129591874

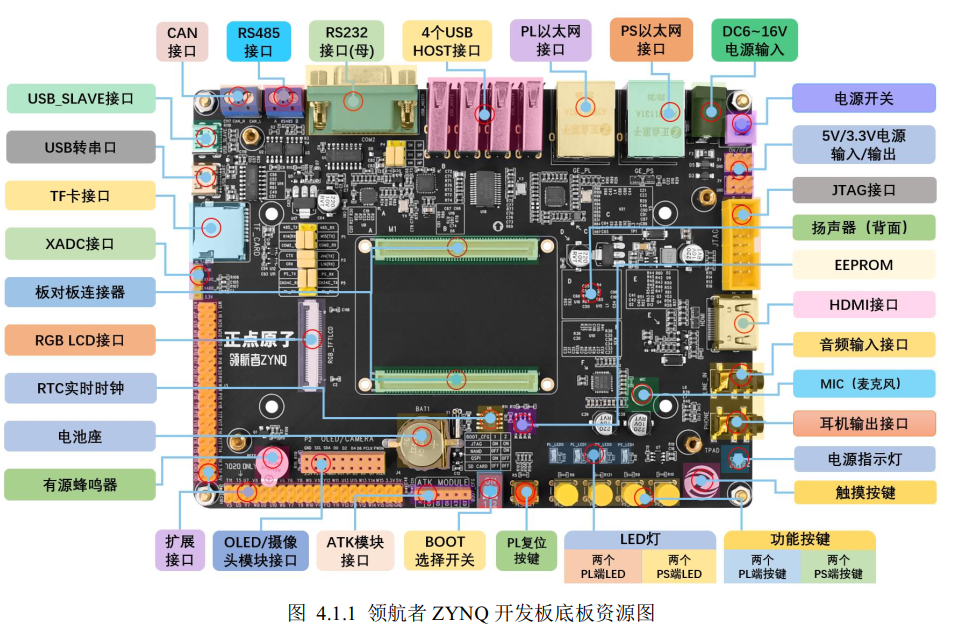

核心板:一般指的是嵌入式系统中的核心处理器板,它是一个完整的计算机系统,包括处理器、内存、外设等,可以作为系统的核心进行开发。通常情况下,核心板上并没有提供太多的外设接口,而是提供了标准的扩展接口,比如GPIO、UART、SPI、I2C、USB等接口,以便于连接各种外部设备和扩展板。核心板的设计一般比较紧凑,功耗低,适用于需要小型化和低功耗的嵌入式系统开发。

底板:(又叫拓展板)则是更为底层的硬件平台,一般指的是一块基础板子,比如说ARM开发板,它的设计比较简单,只提供一些基本的接口,比如UART、SPI、I2C等,用户需要根据自己的需求进行扩展。底板的定位比较低级,主要用于底层驱动和底层算法的开发。

开发板:基于核心板进行扩展和功能实现的平台,开发板是由核心板+拓展板组成。通常会为核心板上提供更多的外设接口,比如摄像头接口、显示屏接口、网口接口等,以方便用户进行系统开发和调试。开发板的设计一般比较灵活,有较多的外设接口,支持快速开发和调试。

IO分配

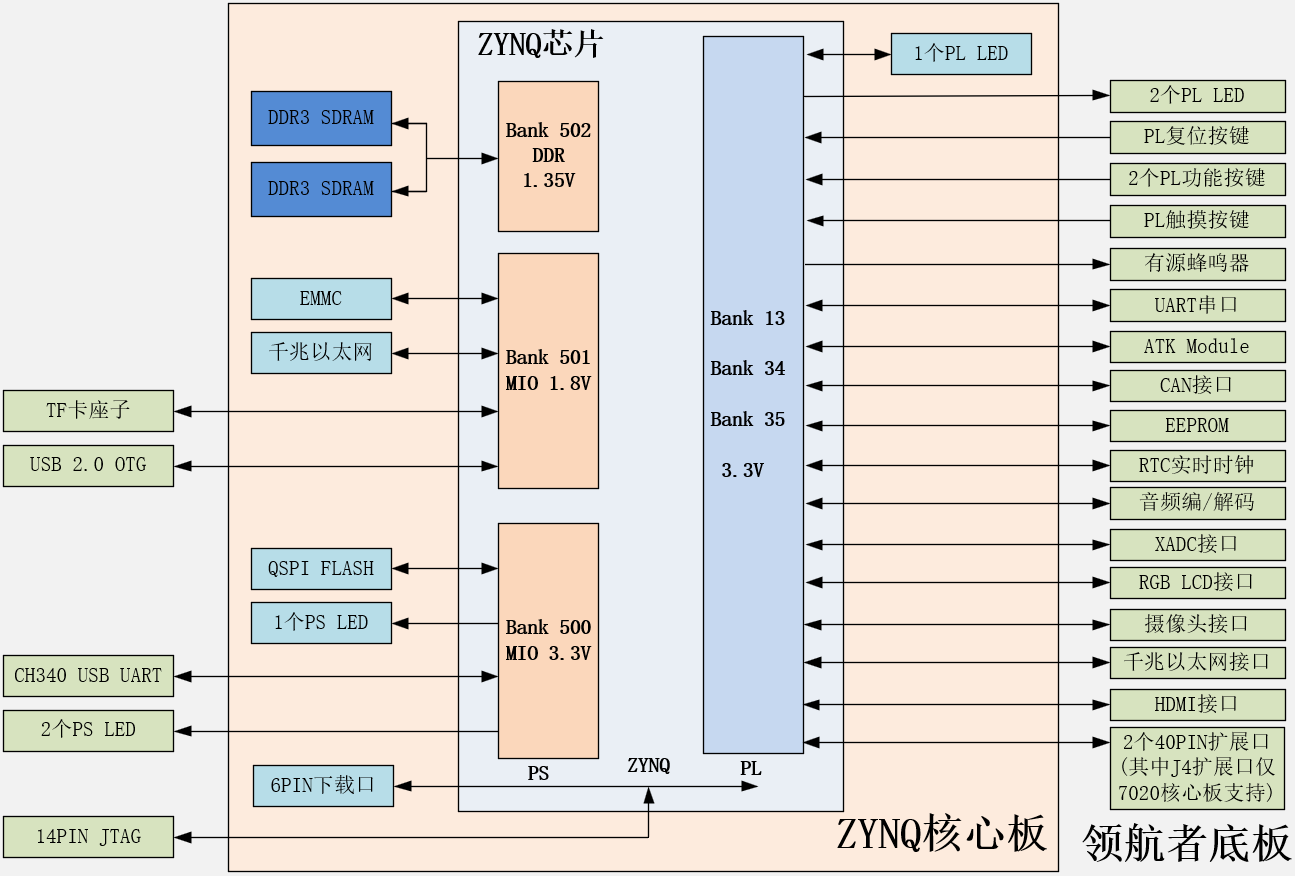

了解器件的 IO 分配方式,有助于我们在硬件设计时根据器件的一些约束,对设计进行合理的 IO 分配,减少硬件出错的可能性。 ZYNQ 的 IO 口分成了 PL 和 PS 两部分,我们将分别介绍 PL 和 PS 两部分的 IO 分配。

概念:Bank

https://zhuanlan.zhihu.com/p/457982520

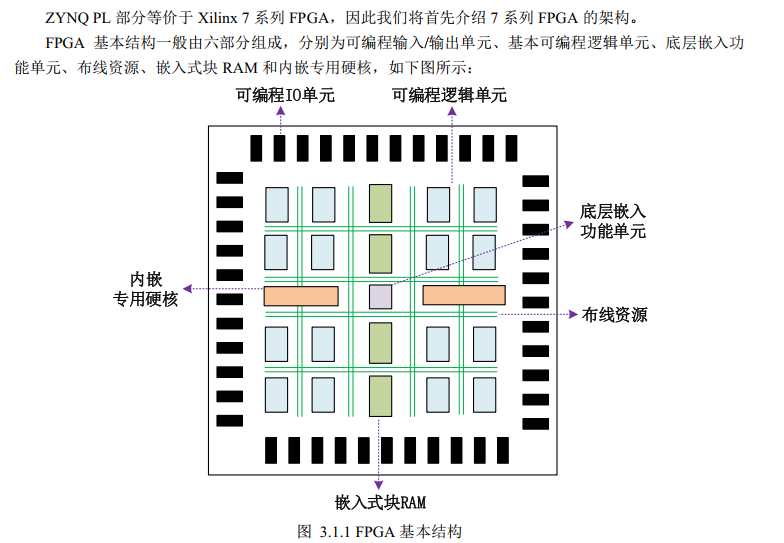

为了便于管理和适应多种电器标准,FPGA的IOB被划分为若干个组(bank),每个bank的接口标准由其接口电压VCCO决定,一个bank只能有一种VCCO,但不同bank的VCCO可以不同。只有相同电气标准的端口才能连接在一起,VCCO 电压相同是接口标准的基本条件。

CPU + FPGA的系统中,CPU的IO电压一般是2.5V而很多其他IC都是3.3V,就可以使用FPGA控制3.3V的IC,而与CPU通讯使用2.5V电平,这样就节省了很多总线转换器。

与 PL 端 IO BANK 不同的是, PS 端的 IO 连接是是相对固定的,用户不能够像 PL 引脚那样,将 PS 端的 IO 随意分配到某个外设。 PS 端外设的 IO 口与 MIO(多路复用 IO)之间,具有固定关系的映射,某个外设的 IO 口可能会映射到不同的 MIO 上,某个 MIO 也有可能会具有多个外设的 IO 口映射到其上面。

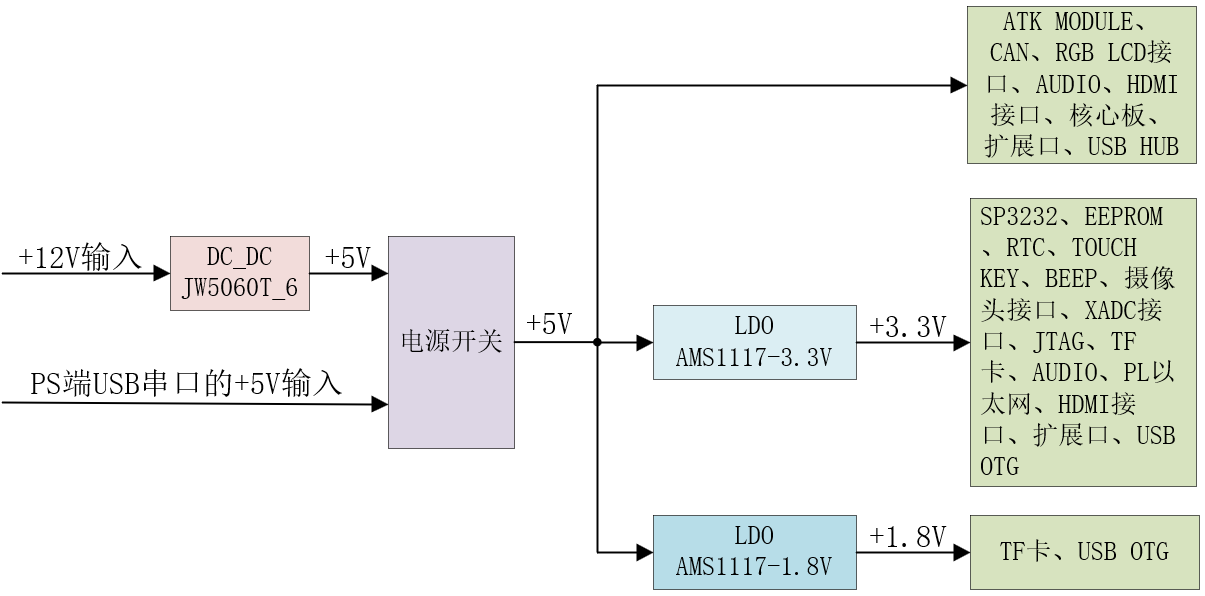

底板电源

概念-引脚复用

管脚复用是指一个引脚具有多个功能,但是在一个时刻只能使用其中一个功能

https://blog.csdn.net/qwaszx523/article/details/59106785

概念:触摸按键

触摸按键在稳定性、使用寿命、抗干扰能力等方面都优于传统的机械按键,被广泛应用于遥控器、 便携电子设备、 楼道电灯开关、 各类家电控制面板等场景 。

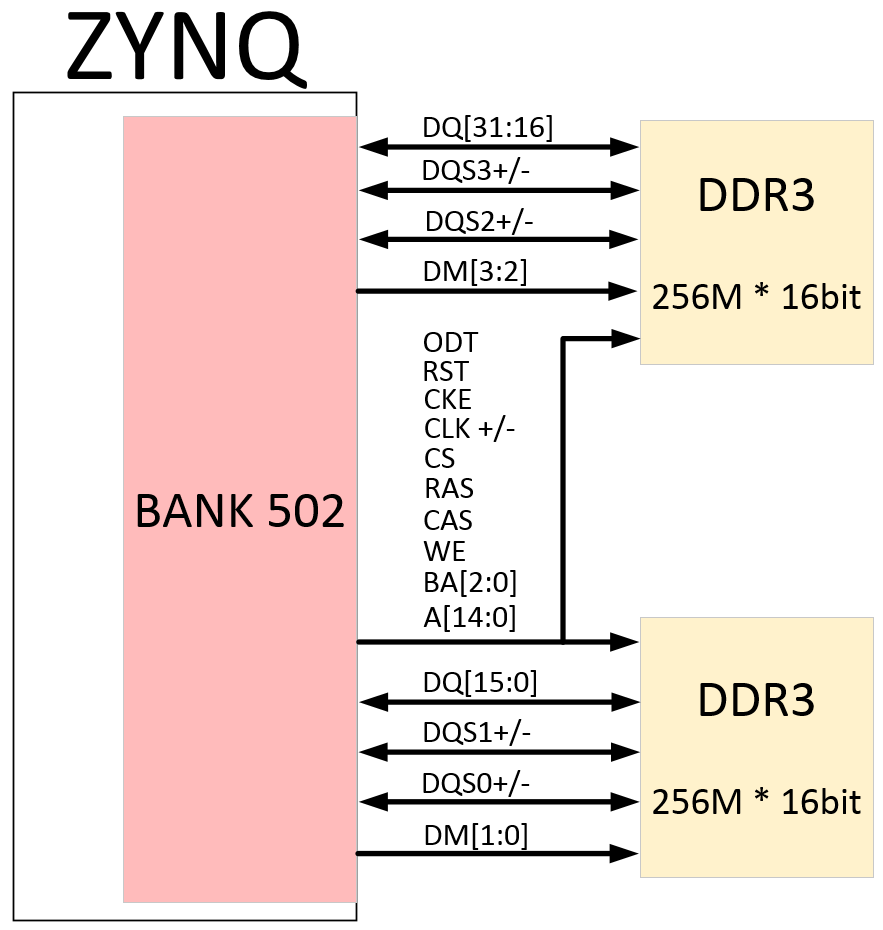

DDR3

两片内存颗粒共享时钟信号、命令信号和地址总线,数据总线、数据选通信号和数据掩码信号各自分开。每片 DDR3 数据位宽为 16 位,两片 DDR3 的组成 32 位位宽的 DDR3 系统,其最大 IO 时钟频率为533MHz,对应的等效数据传输频率为 1066MHz,两个 DDR3 颗粒提供的最大物理带宽为 1066MHz * 32bit*0.9 = 30.7Gbit/s,其中 0.9 是 DDR3 刷新造成的性能损失后的参数。

由于 DDR3 是 PS 部分的存储接口,因此 PL 逻辑需要通过 AXI 接口访问 DDR3。

开发板注意事项

由于 ZYNQ 芯片工作电流较大,而 USB 供电电流最大 500mA, 所以使用 USB 串口进行供电可能会供电不足, 建议大家使用配套的电源适配器供电。

使用某个 IO 口用作其他用处的时候,请先看看开发板的原理图,该 IO 口是否有连接在开发板的某个外设上,如果有,该外设的这个信号是否会对你的使用造成干扰,先确定无干扰,再使用这个 IO。

了解整个硬件对我们后面的学习会有很大帮助,有助于后面的管脚约束(分配),在编写程序的时候,可以事半功倍。

ZYNQ的学习方法

开发板 ;

掌握方法,勤学慎思 ;

了解 ZYNQ 的基本结构

了解 Verilog HDL 基本语法

ZYNQ PS

了解 C 语言的基本语法

了解 PS 端基本的系统框架和外设

软件系统可以被认为是建立于基于硬件的系统上的一个栈,或者说是一系列层,从底至上依次是基础硬件系统(来自 Vivado 的自定义硬件)、板级支持包、 Operating System、 软件应用。

多看看官方的文档和资料,对于 PS 端的软件, xilinx 提供了丰富的库函数,很多时候用户直接调用调用即可,读者要学会利用这些库函数。

多思考,多动手

软件篇

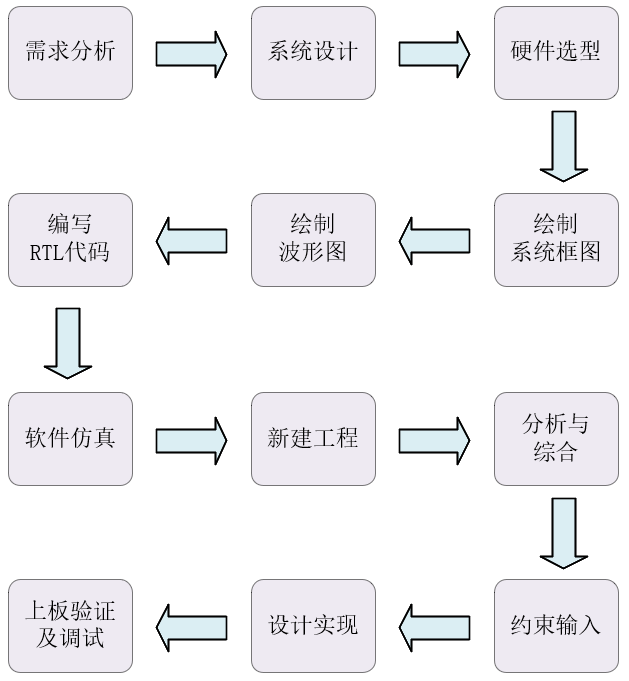

一个完整的 FPGA 的开发流程和仿真过程

实验篇

对于各类实验,先行自己分析一番,然后对照实际方案,再分析研究

1. 基于IIC协议的EEPROM读写测试

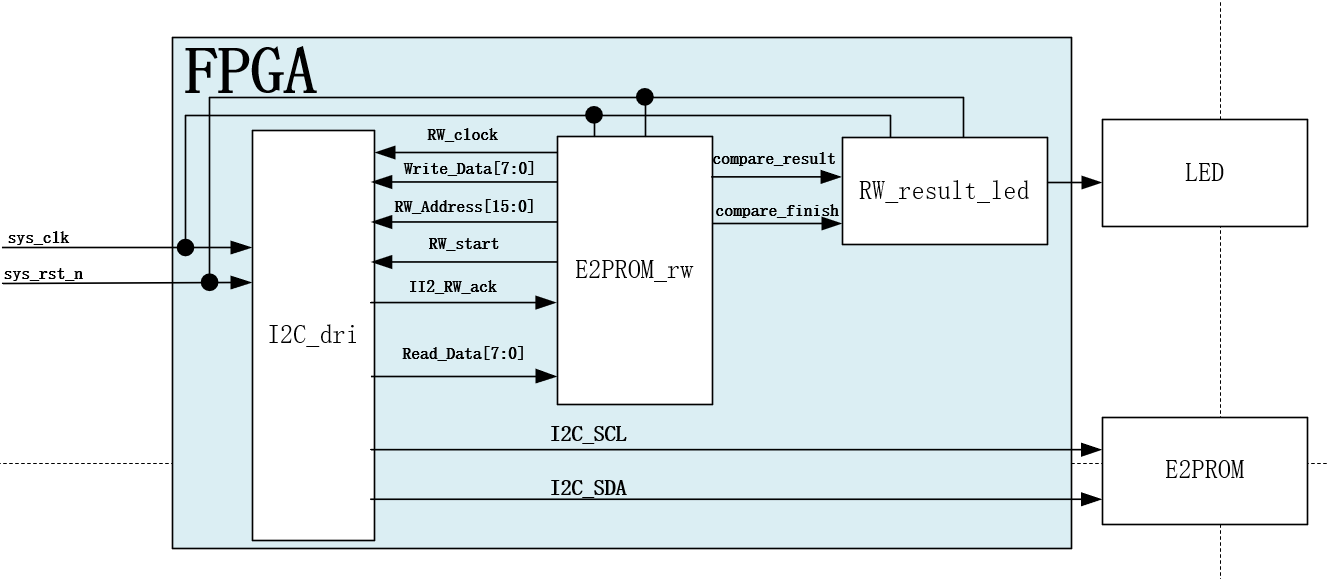

1.1 整体模块设计

目标:对开发板板载的E2PROM进行读写测试,并将读写结果使用LED灯显示出来。

分析:

以FPGA为主机,板载的E2PROM为从机,FPGA通过IIC协议对板载的E2PROM进行读写控制。

--》:IIC驱动模块、E2PROM读写模块

对于读写测试结果,使用LED显示结果表示:

--》: 读写值全部正确(考虑使用页写),LED灯常亮,否则,LED灯闪烁--》E2PROM读写测试结果显示模块

输入端口:系统时钟、系统复位信号

输出端口:LED灯端口、II2串行时钟信号SCL与IIC串行数据信号SDA。

1.2 个人设想

分析各路信号:

I2C_dri和E2PROM_rw之间

RW_clock: I2C通信的时钟,以系统的时钟为基础,通过分倍频得到

Write_Data[7:0]:写入E2PROM的单字节数据;同时根据标志信号RW_start的值,也可传输从机地址

RW_Address[15:0]: 所用E2PROM为多字节地址,需要用两个字节来表示地址

II2_RW_ack:根据II2C协议返回的从机应答信号,标志一个字节的数据的写/读是否有效,是否需要重新传输以及传输下字节的数据

Read_Data[7:0]:读出存在于E2PROM中某一地址的具体一个字节的数据

I2C_dri和E2PROM之间:属于FPGA和外设间的关系,遵循IIC协议

E2PROM和RW_result_led之间

- compare_result: E2PROM内部存在一个缓存比较器,对于读写E2PROM有判断结果后,正确,则传输”1“,错误则传输”0“

- 该信号使用组合或时序逻辑传入RW_result_led都可

- compare_finish:其值为1时,表示读写对比结束,compare_result值有效

RW_result_led和LED之间:属于FPGA和外设间的关系

- 根据传入的信号,在compare_finish=1时,根据compare_result,改变LED灯的闪烁状态,并在其他时刻维持LED灯的闪烁状态

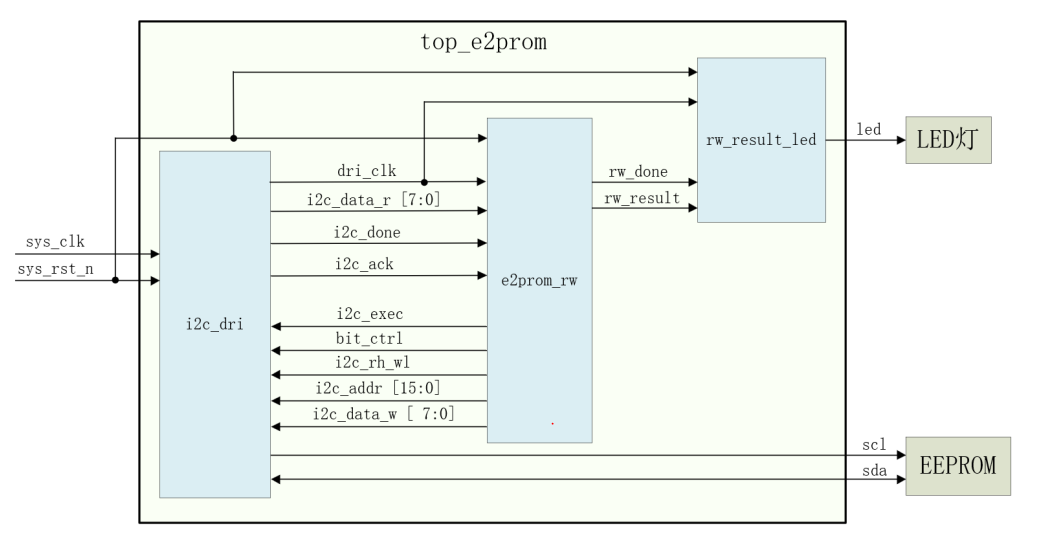

1.3 示例框图

| 模块名称 | 功能描述 |

|---|---|

| i2c_dir | I2C驱动模块,按照I2C协议对I2C设备进行数据读写操作 |

| e2prom_rw | e2prom数据读写模块,生成I2C要写的数据,暂存I2C读出的数据 |

| rw_result_led | e2prom读写测试结果显示模块 |

| top_e2prom | 顶层模块,实例化各子功能模块,连接各模块对应信号 |

1.4 分析自己设计和例程的差异

时钟驱动:

- 1.复位信号应该传入每个子模块,我并未给 rw_result_led 增加 复位信号和时钟信号(设想的是组合逻辑无需?)

- 2.I2C读写时钟应由驱动模块控制产生,而非将系统时钟导入所有模块

I2C驱动模块设计:

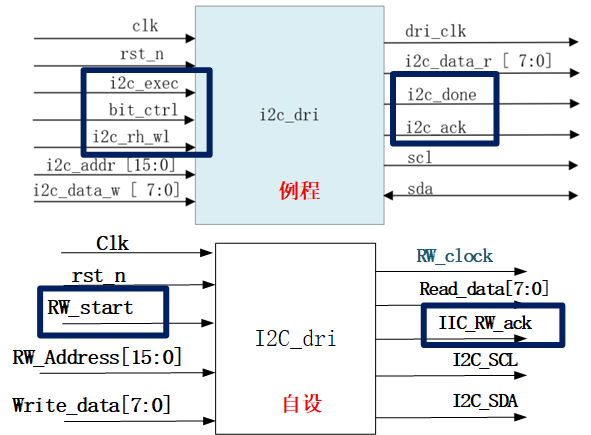

I2C_module_example_self_compare

对比差异,可以看出,对于控制信号,例程有更加详细的设计,表现为

| 信号名 | 位宽 | 方向 | 端口说明 |

|---|---|---|---|

| i2c_exec | 1 | 输入 | I2C触发执行信号 |

| bit_ctrl | 1 | 输入 | 字地址位控制(1: 16b / 0 : 8b) |

| i2c_rh_wl | 1 | 输入 | I2C读写控制信号 |

| i2c_done | 1 | 输出 | I2C一次操作完成 |

| i2c_ack | 1 | 输出 | I2C应答标志 0:应答 1:未应答 |

I2C驱动模块,应尽可能贴近I2C协议,我在这里仅设想了传输的开始和每帧的应答,没有考虑到I2C其他控制、标志信号。