02.时序分析

02.时序分析

什么时候需要时序分析?

- 高速接口

- 针对FPGA的内部功能逻辑代码,如果系统时钟跑的非常高,也应添加时序约束,保证程序正常运行。

一、基本概念

时钟:理想时钟是占空比为50%且周期固定的方波。实际电路中输入给FPGA的晶振时钟信号是正弦波,然波形不影响FPGA对时钟的识别。

时钟抖动(Clock Jitter):是指相对于理想时钟沿,实际时钟存在存在的不随时间积累的、时而超前、时而之后的偏移称为时钟抖动(时钟脉冲宽度发生暂时变化,时钟周期或大或小)

随机抖动

固定抖动

时钟偏差/偏移(Clock Skew): 是指同一个时钟域内的时钟信号到达数字电路各个部分所用的时间差异。

- 正偏差:时钟同数据同向传播,使得采样数据的有效时钟沿较之发送数据的有效时钟沿较晚到达

- 负偏差:时钟域数据相向传播,使得采样数据的有效时钟沿较之发送数据的有效时钟沿较早到达

Clock Uncertainty:时钟的不确定性

Clock Uncertainty = Clock Skew + Clock Jitter

对Clock Uncertainty 添加约束,即为了让时序分析更贴近真实的电路设计

对于频率较高的时钟,Clock Uncertainty 设置相对可较小;

频率较低或经过分频的时钟,可增大。

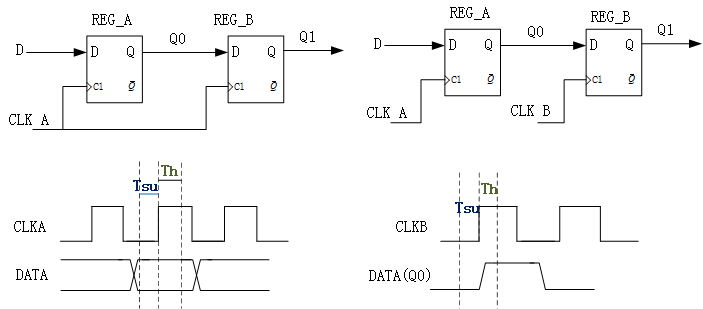

同步电路和异步电路

Tsu : 建立时间,即在时钟上升沿之前数据必须稳定的最短时间,若不满足,数据无法进入寄存器,寄存器的数据采样会失败

Th : 保持时间,即时钟上升沿之后数据必须稳定的最短时间,若不满足,同样

二、时序分析的基本公式

https://blog.csdn.net/zz_Caleb/article/details/84453792

https://blog.51cto.com/u_16213603/10577001

2.1 时序分析的基本路径

管脚输入和寄存器之间的路径 pin2reg

寄存器和寄存器之间的路径 reg2reg

寄存器和管脚输出之间的路径 reg2pin

管脚输入和管脚输出之间的路径 pin2pin

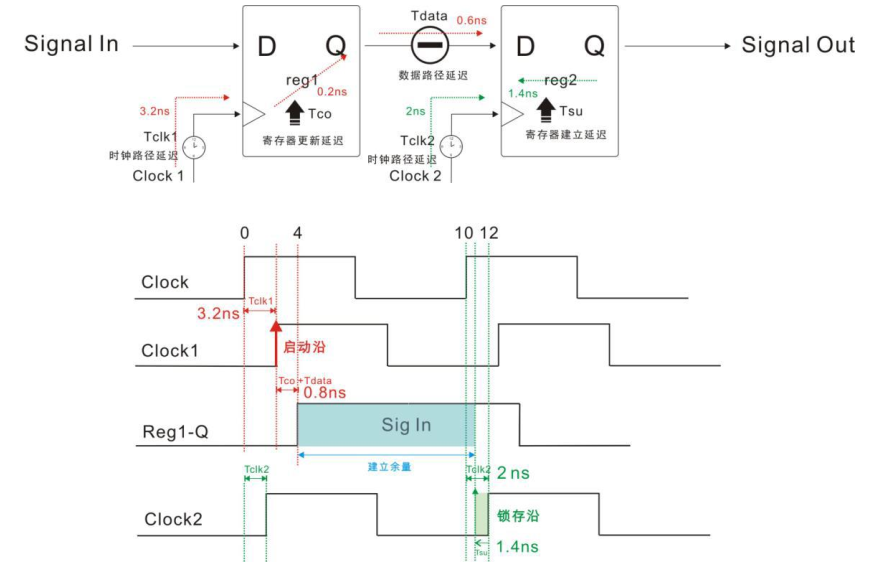

2.2 数据到达时间和时钟到达时间

数据在发送沿发送之后,经过多长时间会到达接收寄存器的数据端口,即到达regb的D端口的时刻,这个时刻就是数据到达时间。

参考(基准)时间点:一般选择 launch edge 作为零时刻基准点。

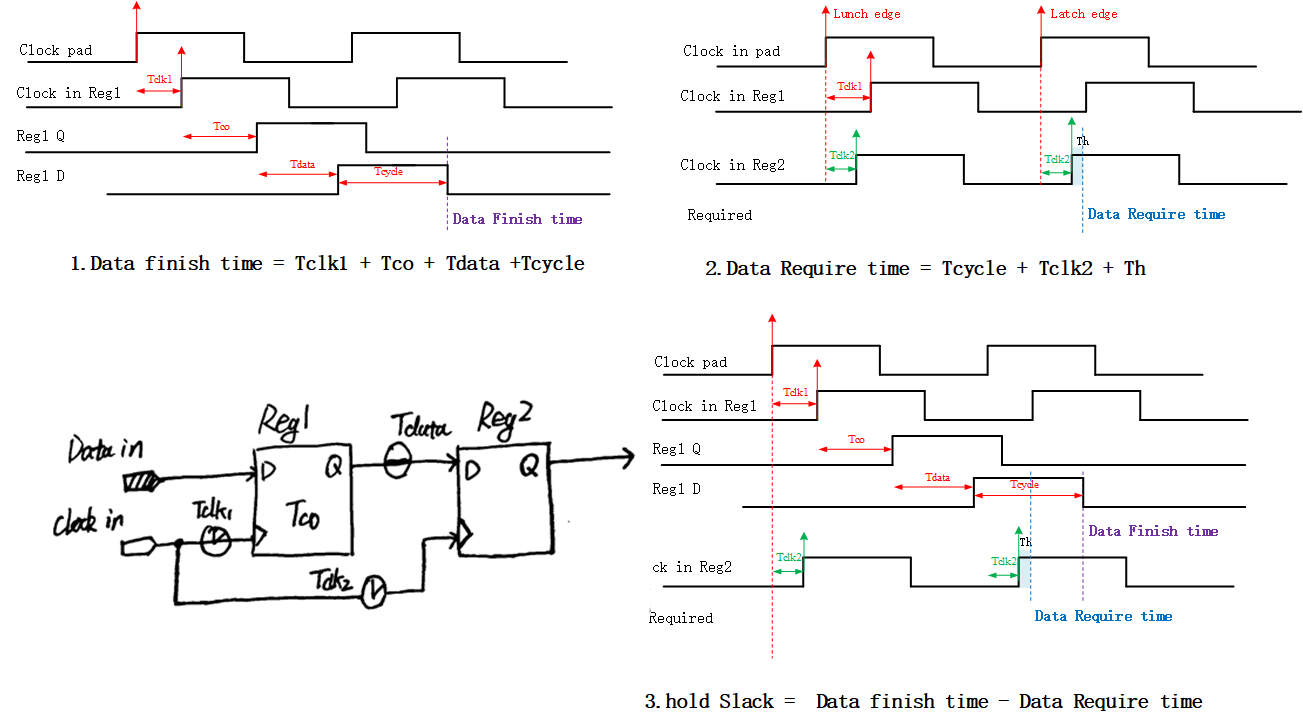

公式1:

数据到达时间 = 启动沿时间+ Tclka + Tco + Tdata

公式2:

时钟到达时间 = 采样沿时间+Tclkb

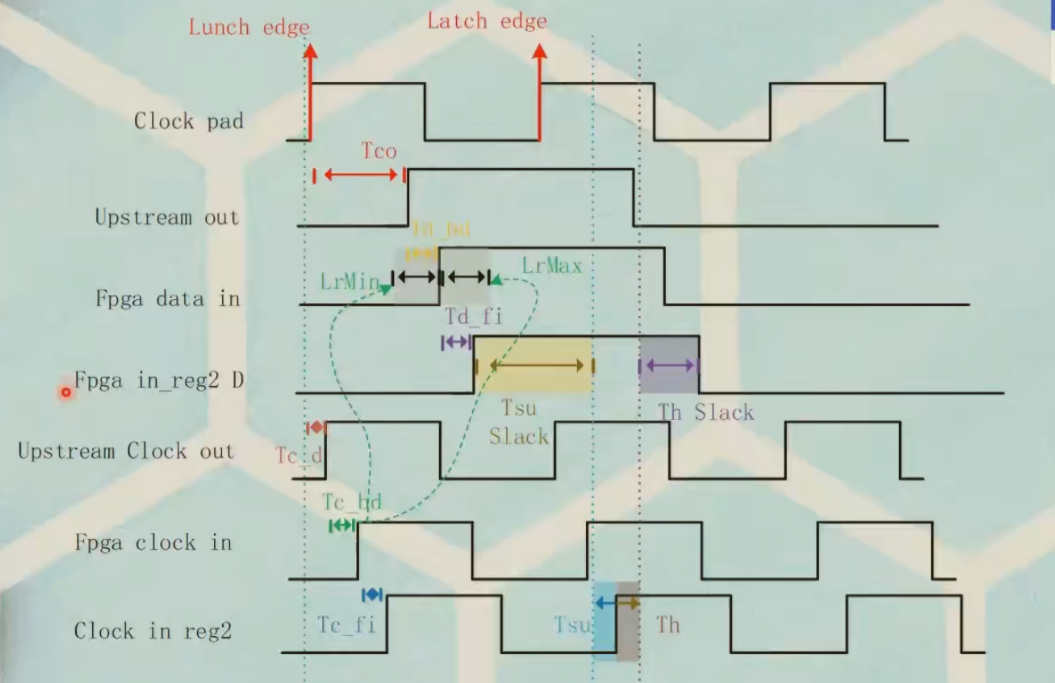

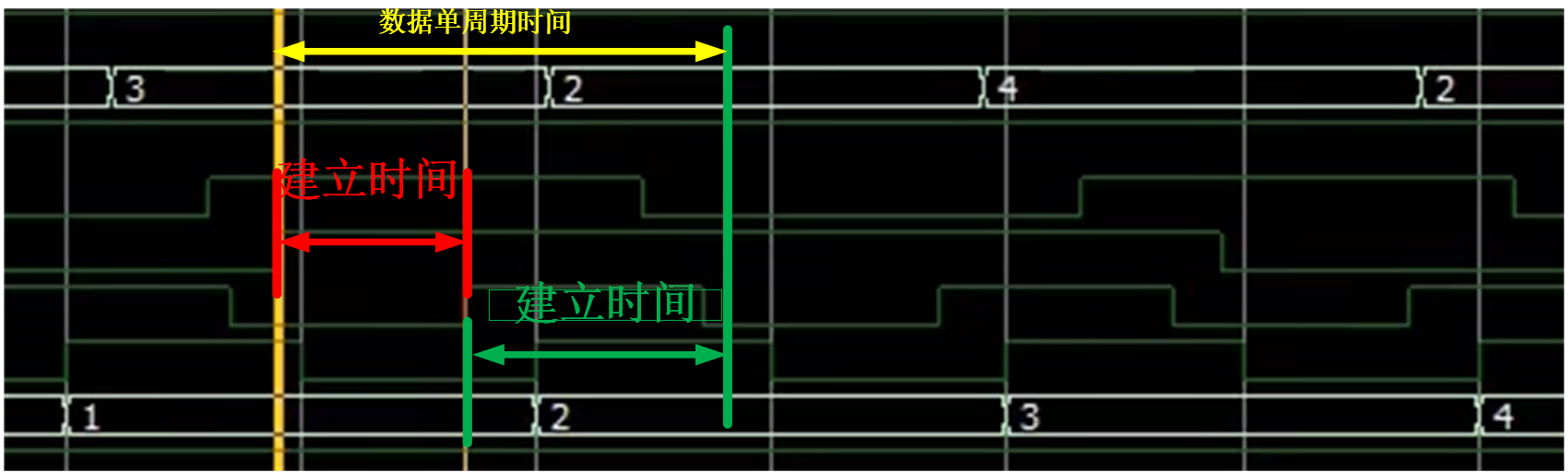

3. 建立时间的裕量(Setup slack)

计算:

数据达到时间 = 启动沿时间+Tclk1+Tco+Tdata

数据锁存时间 = 锁存沿时间+Tclk2-Tsu

建立裕量 = 数据锁存时间- 数据到达时间

判断:

建立裕量>0 ? 合格建立关系 : 建立关系不满足,数据采样会出错;

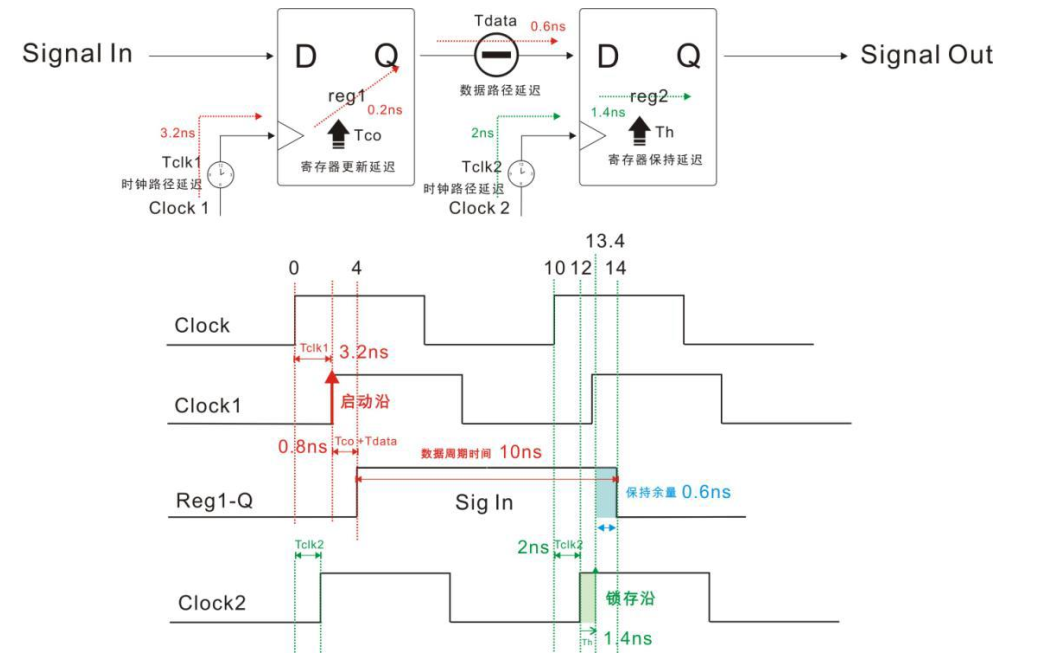

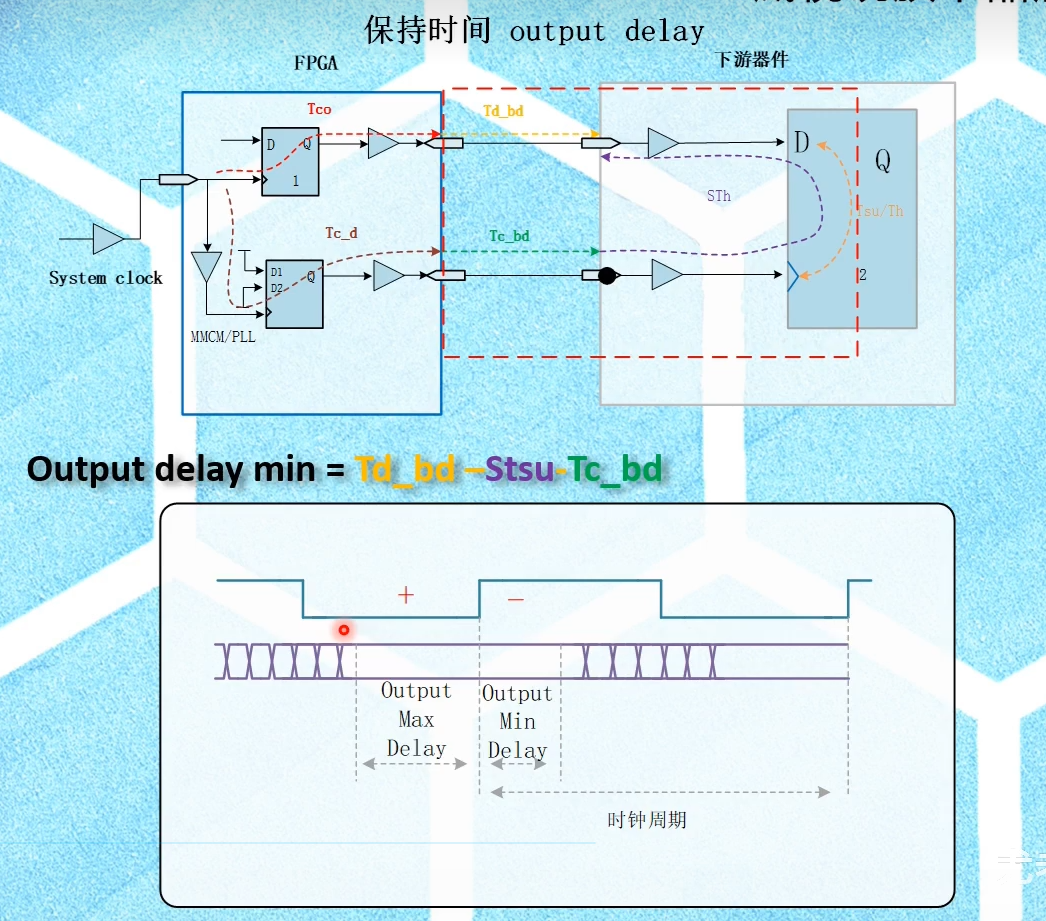

4.保持时间的裕量(Hold slack)

计算:

数据保持时间 = 启动沿时间 + Tclk1 + Tco + Tdata + 数据周期时间

数据锁存(读取)时间 = 锁存沿时间+Tclk2+Th

保持裕量 = 数据保持时间 - 数据锁存(获取|读取)时间

判断:

保持裕量>0 ? 合格保持关系 : 保持关系不满足,数据采样会出错;

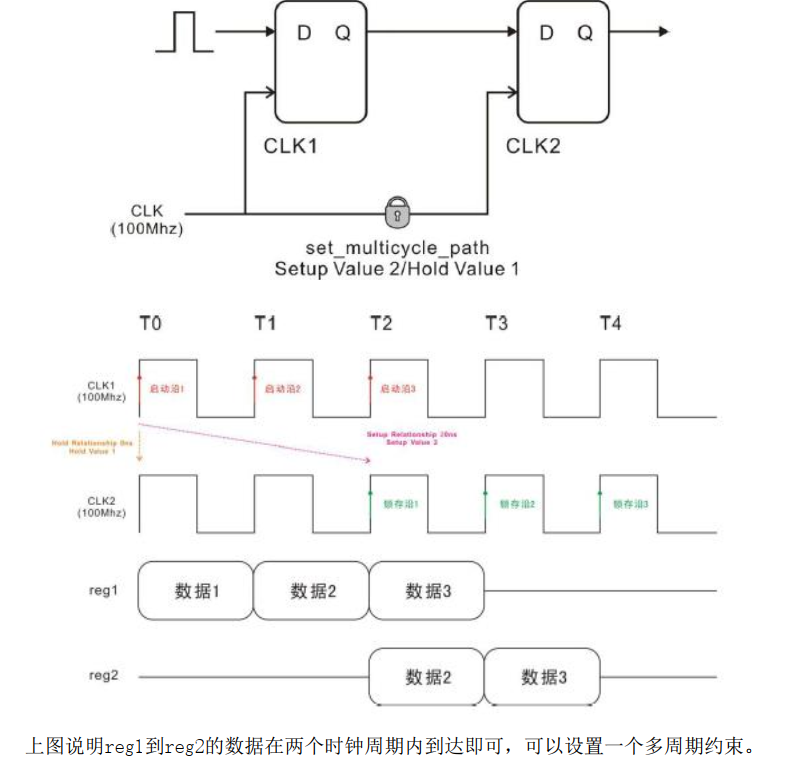

5. 多周期路径(Multicycle Paths)

按照单周期关系考虑数据路径是否满足,存在以下的忽略情况:

- 一些数据不需要在下一个时钟周期就稳定下来,可能在数据发送后几个时钟周期菜起作用

- 一些数据经过的路径太复杂,延时太大,不可能在下一个时钟周期稳定下来,必须要在数据发送后数个时钟周期才被采样。

不设置多周期路径约束的后果:

- 按照单周期路径检测,虚报时序违规;

- 布局布线工具按照单周期路径的方式执行,虽满足了时序规范,然过分优化了本应该多个周期完成的操作,造成过约束。

- 过约束会侵占本应该让位于其他逻辑的布局布线资源,存在造成其他关键路劲的时序违规或时序裕量变小。

三、 FPGA 器件时序模型

由于FPGA芯片加工时存在不同的参数差异,这些参数差异导致了时序分析需要分析更多种情况,影响时序分析的原因是PVT。

3.1 PVT

PVT是指芯片工艺(Process)、电压(Voltage)和温度(Temperature)。

概念:芯片的Process corner,工艺角

不同的芯片晶圆和不同的晶圆批次之间,因为掺杂、刻蚀、温度等外界因素导致警惕管参数的变化范围较大。为减小设计困难度,需要将器件性能限制在某个范围内,并报废超出这个范围的芯片篇,来严格控制预期的参数变化。工艺角和性能范围有关。

PVT 和时序模型关系很紧密,也就是说不同的 PVT 参数,芯片的时序模型都是有差异的。

时序分析工具会依据仿真需求,使用不同的 PVT 组合,用于 STA 分析,因为实际的ASIC/FPGA 芯片也存在不同的 PVT 组合,每种组合的时序模型是不一样的,因此 STA 需要分析各种情况下的组合。

一般时序分析会涉及到如下三种情况:

最好的条件( Best Case) ——速度最快的情况;

最坏的条件( Worst Case) ——速度最慢的情况;

典型的条件( Typical Case) ——速度介于最快和最慢之间;

三种情况分别对应如下细节:

- BCF(Best Case) : fast process,lowest temperature,high voltage

- WCS(Worst Case) : slow process,high temperature,lowest voltage

- TYP(Typical Case) : typical process,nominal temperature,nominal voltage

时序分析工具通过 Worst corner 来保证建立时间的时序,通过 Best corner 来保证保持时间的时序。由于一般情况下设计以建立时间违例为主,所以时序分析工具默认使用slow corner。

3.2 基本单元与Paths

3.2.1 基本单元

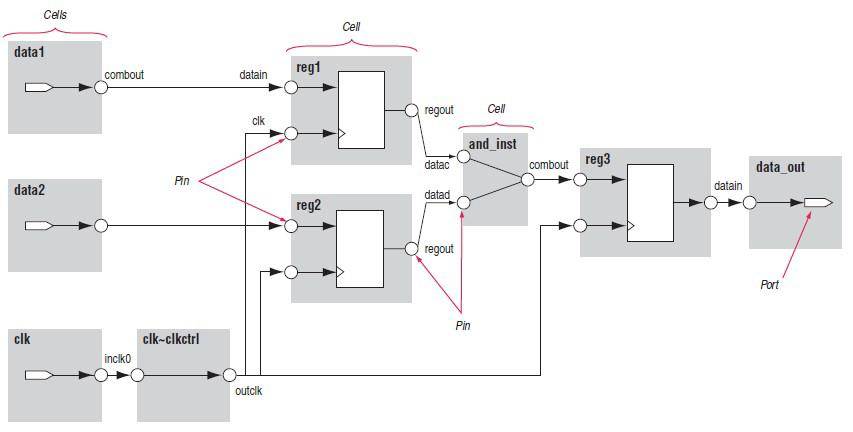

FPGA开发工具需读入布局布线后的王彪才能进行时序分析,读入的网表由以下一系列的基本单元构成:

| 基本单元 | 说明 |

|---|---|

| cell | PFGA网表种最普遍的个体。FPGA种可以找到的寄存器,片上RAM,PLL资源,硬件乘法器等逻辑资源 |

| Pin | Cell 进出口 |

| Net | Pins 之间的连线 |

| Port | 顶层模块的顶层输入输出口 |

Cells: Altera 器件中的基本结构单元( 例如, 查找表、寄存器、 IO 单元、 PLL 、存储器块等)

Pins: Cell 的输入输出端口。注意:这里的 Pins 不包括器件的输入输出引脚。

Nets:同一个 Cell 中,从输入 pin 到输出 pin 经过的逻辑。注意,网表中连接两个相邻 Cell 的连线不被看作 Net,而被看作同一个点,等价于 Cell 的 pin 。虽然连接两个相邻 Cell 的连线不被看作 Net,但这个连线还是有其物理意义的,即等价于 FPGA 器件中的一段布线逻辑,会引入一定的延迟。

Ports:顶层逻辑的输入输出端口。对应已经分配的器件引脚。

网表例子

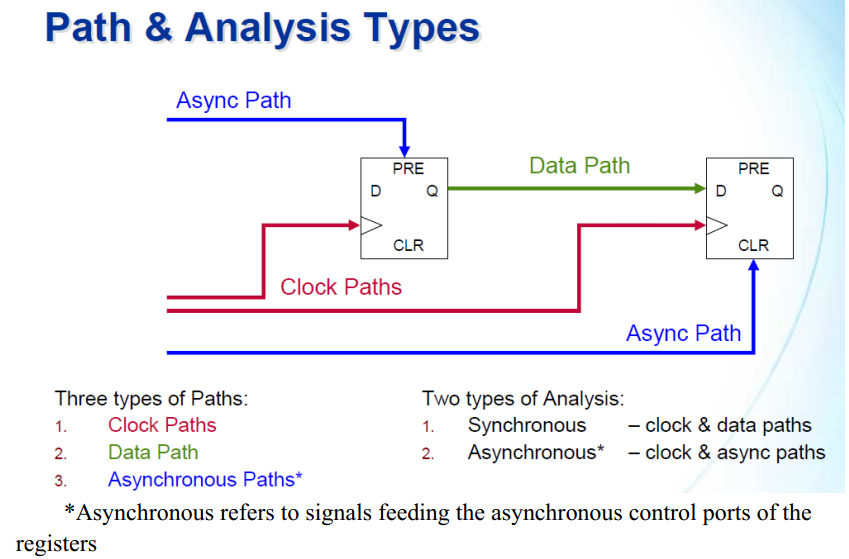

3.2.2 Paths

- Clock paths :从 Clock port 或内部生成的 clock pin 到寄存器Cell 的时钟输入Pin

- Data paths : 从输入 Port 到寄存器 Cell 的数据输入 pin ,或从寄存器 Cell 的数据输出 pin 到另一个寄存器 Cell 的数据输入 pin

- Asynchronous paths:从输入 Port 到寄存器 Cell 的异步输入 pin ,或从寄存器Cell 的数据输出 pin 到另一个寄存器 Cell 的异步输入 pin

四、FPGA 时序约束的几种方法

对自己的设计的实现方式、时序要求、目标器件的资源分布、结构和FPGA工具执行约束的效果越了解,则对设计的时序约束目标就会越清晰,相应地,设计的时序收敛过程就会更加可控。

4.1 时钟约束

时钟约束是最基本的一个约束,因为 FPGA 工具是不知道你要跑多高的频率的, 你必要要告诉工具你要跑的时钟频率。 时钟约束也就是经常看到的 Fmax, 因为 Fmax 是针对“最差劲路径”,也就是说,如果该“最差劲路径”得到好成绩,那些不是最差劲的路径的成绩当然比“最差劲路径”好。 Best case 的 Fmax 评估比起 Worst case 有更好的表现(也更接近实体的 Fmax 评估)。

4.2 时钟约束+时序例外约束

有时候一个设计中,存在多个时钟,光有时钟约束是不够的,还需要加一些例外约束,时序例外约束包括 FalsePath 、 MulticyclePath、 MaxDelay、 MinDelay。但这还不是最完整的时序约束。如果仅有这些,说明时序分析思路还局限在 FPGA 芯片内部。

4.3 系统时钟约束+时序例外约束+I/O约束

一般 FPGA 设计都是有 IO 管脚的,这些 IO 管脚也需要相关约束, IO 约束包括引脚分配位置、空闲引脚驱动方式、外部走线延时(InputDelay 、 OutputDelay)、上下拉电阻、驱动电流强度等。加入 I/O 约束后的时序约束,才是最完整的时序约束。

FPGA 作为 PCB 上的一个器件,是整个 PCB 系统时序收敛的一部分。 FPGA 作为 PCB 设计的一部分,是需要 PCB 设计工程师像对待其他器件一样,阅读并分析其 I/O 时序图的。 FPGA不同于一般器件之处在于,其 I/O Timing 在设计后期可以于一定范围内调整。虽然如此,最好还是在 PCB 设计前期给与充分的考虑并归入设计文档。正因为 FPGA 的 I/O Timing 会在设计期间发生变化,所以准确地对其进行约束是保证设计稳定可控的重要因素。许多在 FPGA 重新编译后, FPGA 对外部器件的操作出现不稳定的问题都有可能是由此引起的。

好的时序是设计出来的,不是约束出来的 。好的约束必须以好的设计为前提。没有好的设计,在约束上下再大的功夫也是没有意义的。不过,通过正确的约束也可以检查设计的优劣,通过时序分析报告可以检查出设计上时序考虑不周的地方,从而加以修改。通过几次“分析—修改—分析” 的迭代也可以达到完善设计的目标。应该说,设计是约束的根本,约束是设计的保证,二者是相辅相成的关系。

五、时序分析圣经

《Static Timing Analysis for Nanometer Designs A Practical Approach》

概念及引入

- Nanometer Designs 纳米设计

In semiconductor devices, metal interconnect traces are typically used to make the connections between various portions of the circuitry to realize the design.

在半导体器件中,金属互连走线通常用于在电路的各个部分之间建立连接以实现设计。

While the noise and coupling effects are negligible at older generation technologies, these play an important role in nanometer technologies. Thus, the physical design should consider the effect of crosstalk and noise and the design verification should then include the effects of crosstalk and noise.

虽然噪声和耦合效应在老一代技术中可以忽略不计,但它们在纳米技术中发挥着重要作用。因此,物理设计应考虑串扰和噪声的影响,然后设计验证应包括串扰和噪声的影响。

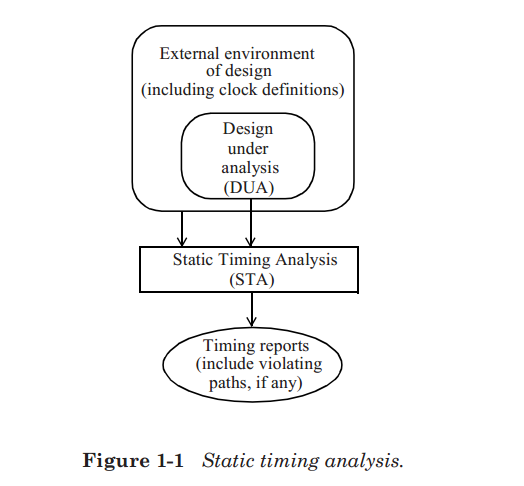

- STA

The STA is static since the analysis of the design is carried out statically and does not depend upon the data values being applied at the input pins.

STA是静态的,因为对设计的分析是静态进行的,不依赖于在输入引脚处应用的数据值。

Given a design along with a set of input clock definitions and the definition of the external environment of the design, the purpose of static timing analysis is to validate if the design can operate at the rated speed.

给定一个设计以及一组输入时钟定义和该设计的外部环境定义,静态时序分析的目的是验证该设计是否可以在额定速度下运行。

A setup check ensures that the data can arrive at a flip-flop within the given clock period.

A hold check ensures that the data is held for at least a minimum time.

So that there is no unexpected pass-through of data through a flip-flop: that is, it ensures that a flip-flop captures the intended data correctly. These checks ensure that the proper data is ready and available for capture and latched in for the new state.

这样就不会有意外的数据通过触发器传递:也就是说,它确保触发器正确捕获预期的数据。这些检查确保适当的数据已经准备好,并可用于捕获和锁定新状态。

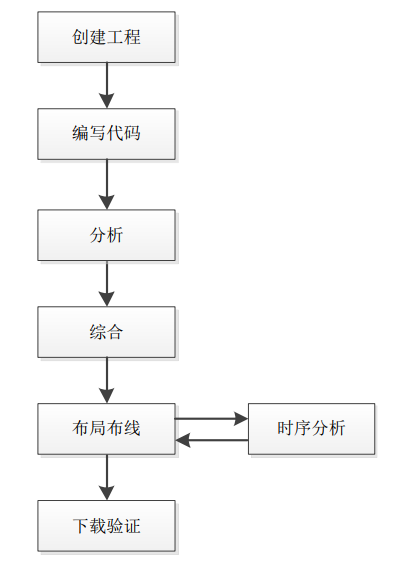

设计流程及不同的阶段

FPGA和基于CMOS的流程本质一样

异步设计

One may be more interested in timing from one signal in the design to another as opposed to doing setup and hold checks which may be non-existent.

STA的原理也适用于异步设计。人们可能对设计中从一个信号到另一个信号的时序更感兴趣,而不是进行可能不存在的设置和保持检查。

- point to point timing checks 点对点定时检查

- skew checks

noise analysis 噪声分析

The noise analysis to analyze the glitches induced due to coupling are applicable for any design - asynchronous or synchronous

噪声分析用于分析由耦合引起的故障,适用于任何设计-异步或同步

其他方面:

Limitations of Static Timing Analysis 静态时序分析的局限性

Power Considerations 功率因素

Reliability Considerations 可靠性方面的考虑

简述

While static timing analysis may appear to be a very simple concept on the surface, there is a lot of background knowledge underlying this analysis.

The underlying concepts range from accurate representation of cell delays to computing worst path delays with minimum pessimism.

The concepts of computing cell delays, timing a combinational block, clock relationships,multiple clock domains and gated clocks form an important basis for statictiming analysis.

Writing a correct SDC for a design is indeed a challenge.

书籍目录

1.representing accurate cell delays

2.Estimating or computing exact interconnect delays and their representation in an effective manner

以有效的方式估计或计算准确的互连延迟及其表示

3.Computing delay of a path composed of cells and interconnect

计算由单元和互连组成的路径的延迟

4.Signal integrity, that is the effect of signal switching on neighboring nets and how it impacts the delay along a path

信号完整性,即信号交换对相邻网络的影响以及它如何影响路径上的延迟

5.Accurately representing the environment of the DUA with clock definitions and path exceptions

精确地表示具有时钟定义和路径异常的DUA环境

6.The details of the timing checks performed in STA

在STA中执行的定时检查的详细信息

7.Modeling IO timing across variety of interfaces

跨各种接口建模IO时序

8.advanced timing checks such as on-chip variations, clock gating checks, power management and statistical timing analysis

先进的定时检查,如芯片上的变化,时钟门控检查,电源管理和统计定时分析

六、Vivado 实际操作

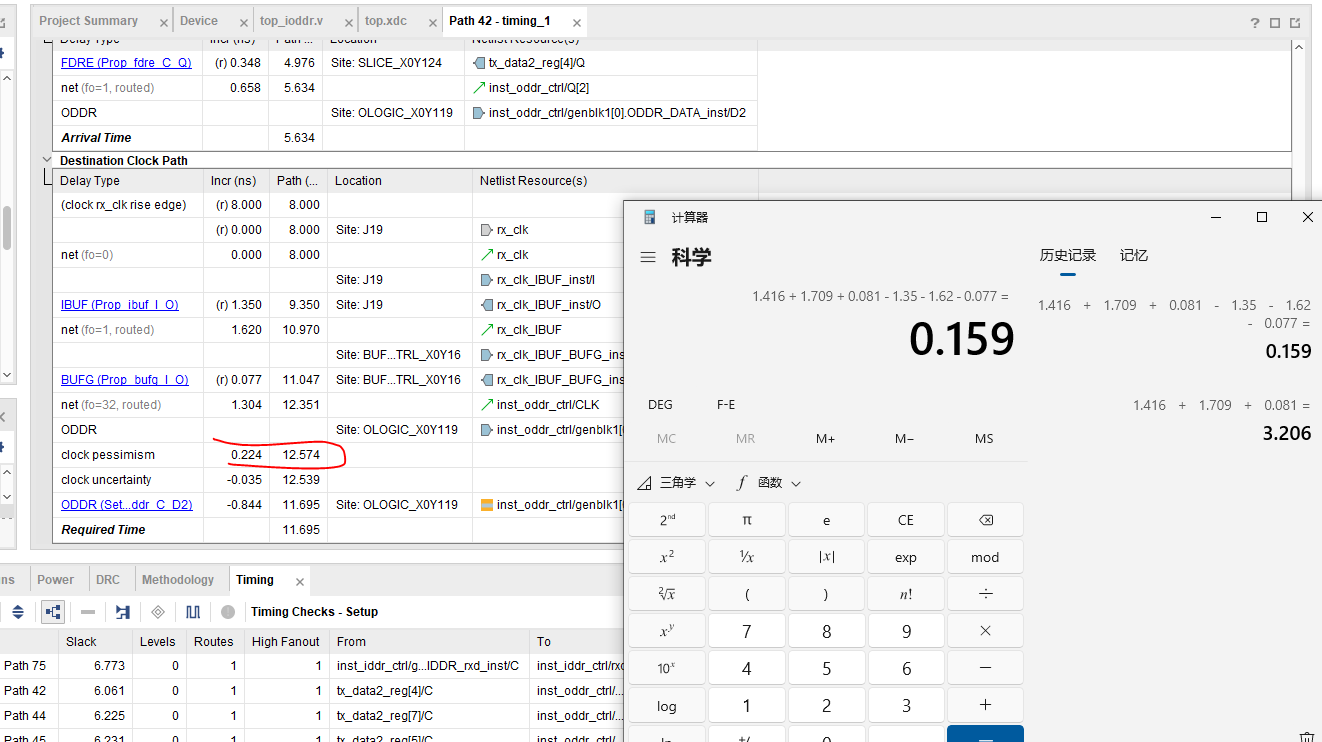

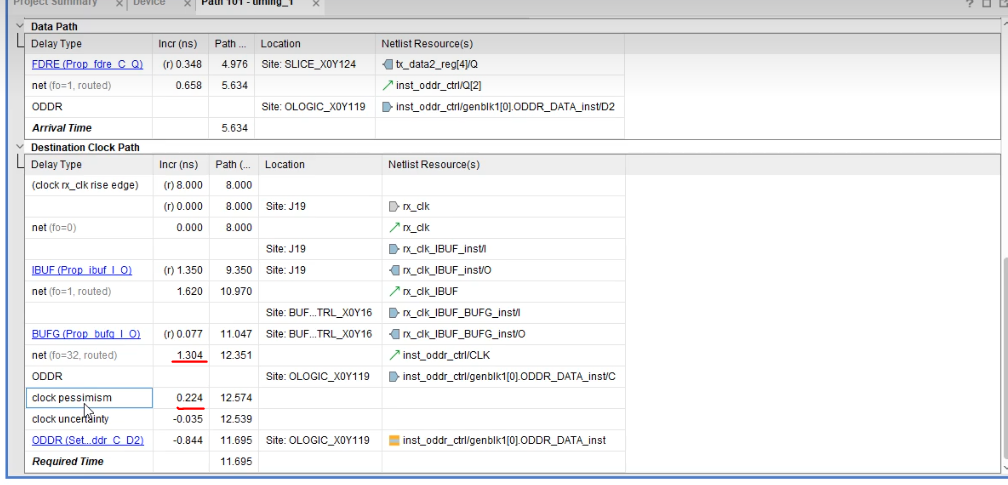

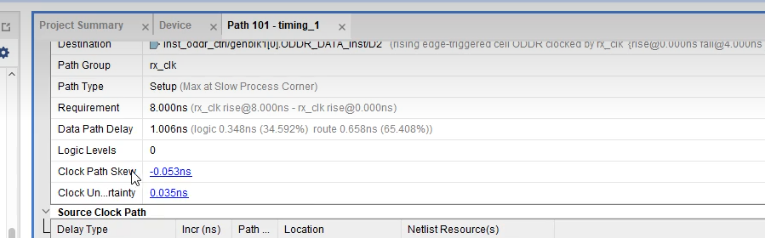

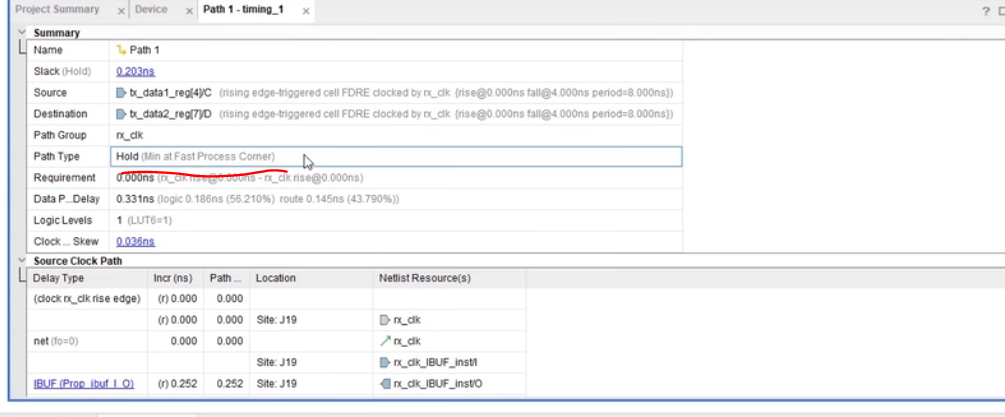

6.1 第1,2讲,计算(建立时间裕量)与时序报告

结果不一致,但计算思路如此,抛开共同的路径,考虑最小的悲观。

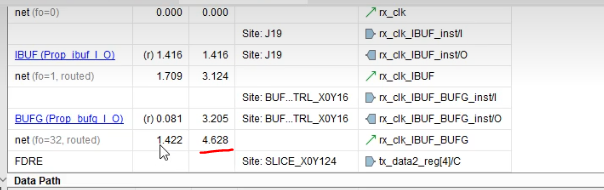

认为 共同路径:时钟管脚输入到BUFG输出,

但是由BUFG输出到源寄存器的clk端与到目的寄存器的clk端这两个部分仍存在共同路径

即下图 1.304-1.423-= 时钟偏斜(skew)+共同路径的补偿值= -0.053 + -0.066

11.047-8-3.205-0.066=-0.224

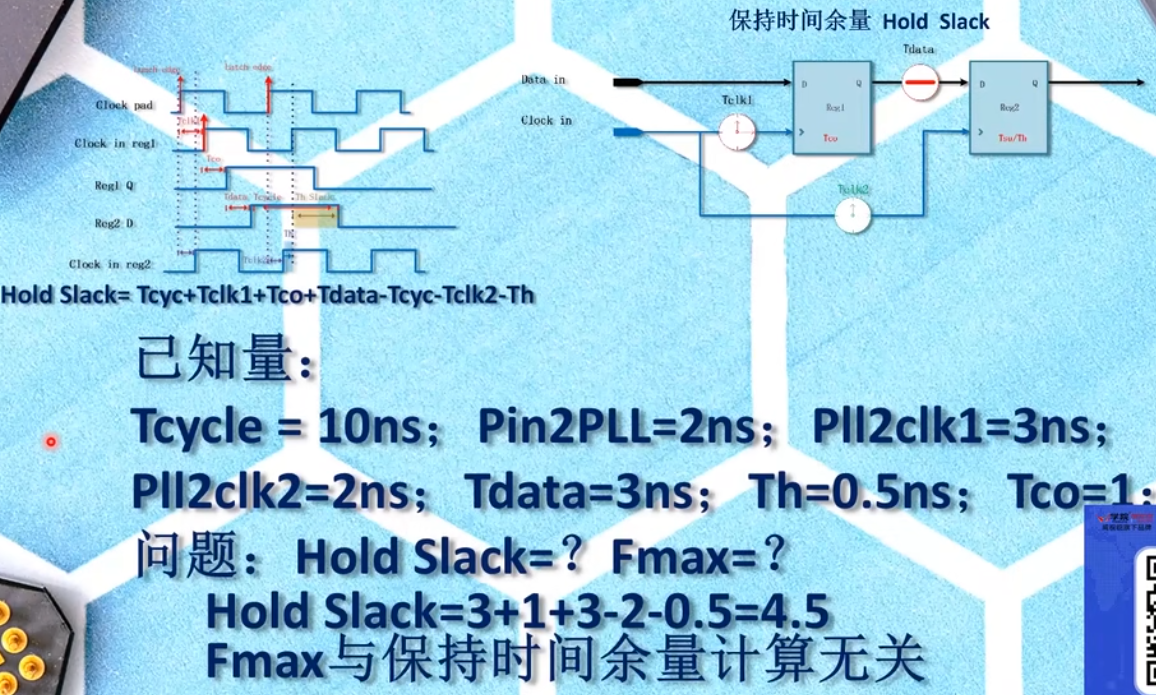

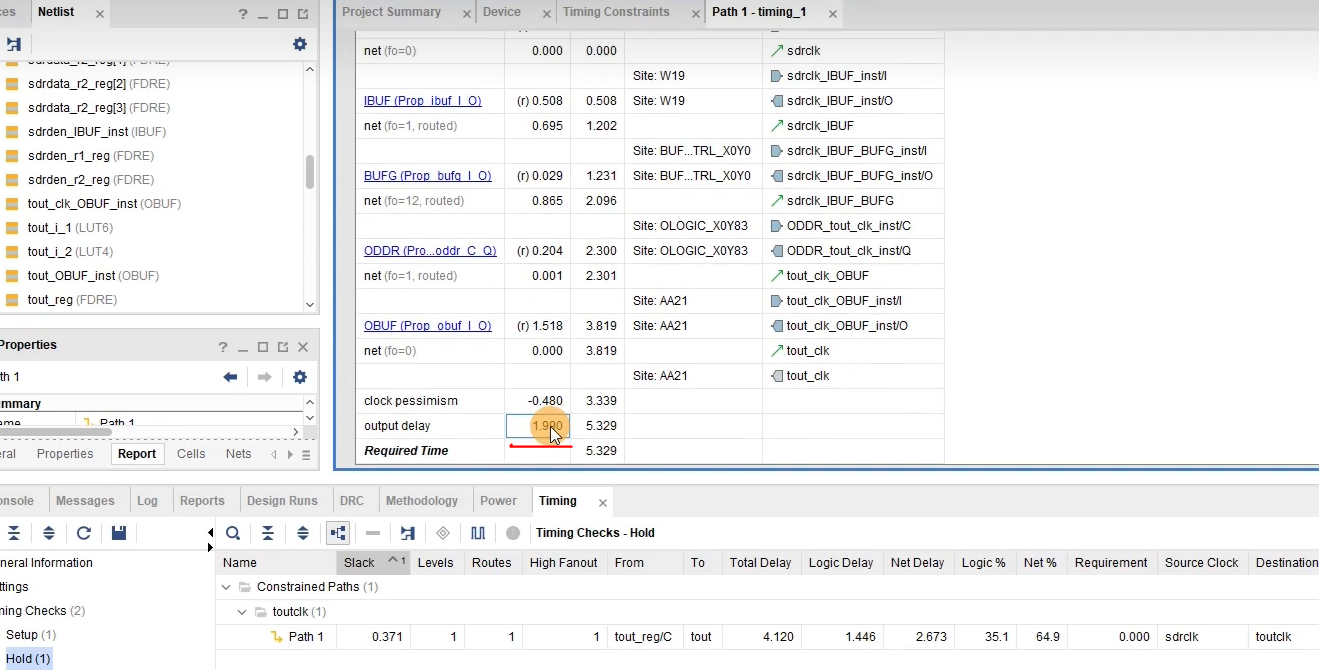

6.2 第3讲 寄存器间分析-保持时间裕量

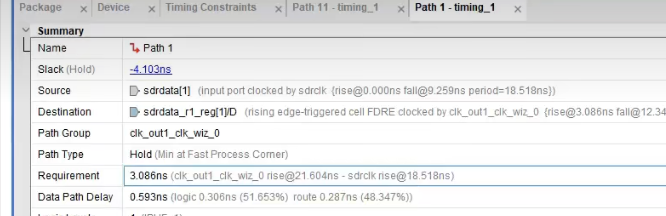

hold slack = Tcycle + Tclk1 + Tco +Tdata - Tcycle-Tclk2-Th

通过改善保持时间,能否提高整个系统的运行时钟频率?

由上述可知,保持时间裕量和时钟周期Tcycle无关

hold slack 和 setup slack 是一对矛盾体。

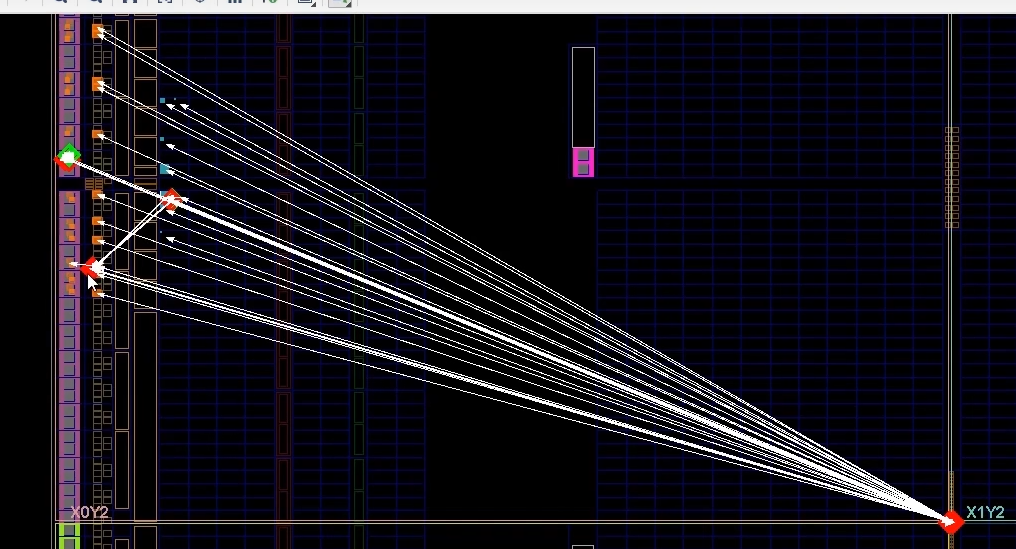

没有分配具体管脚的时序分析报告,没有意义。

hold slack = Tcycle + Tclk1 + Tco +Tdata - Tcycle-Tclk2-Th=Tclk1 + Tco +Tdata-Tclk2-Th

考虑 Tdata 取最小值,则保持时间裕量越小,建立时间裕量越大,整体系统可运行的时钟频率越高

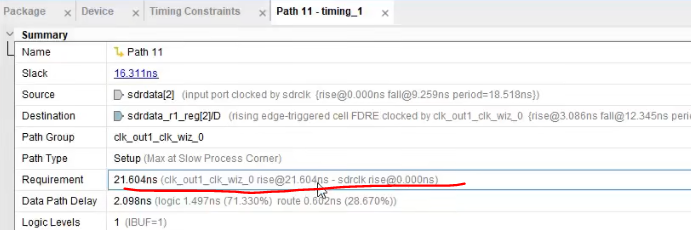

对于setup slack 分析时,Max at Slow Process Corner 即 考虑 Tdata 最大

当我们建立了一个对于时钟的约束后(绑定了正确的管脚),布局布线工具就会努力去使得电路既满足保持时间的裕量,也满足建立时间的裕量。

6.3 第4,5,6,7,8,9讲 IO时序分析-输入延迟

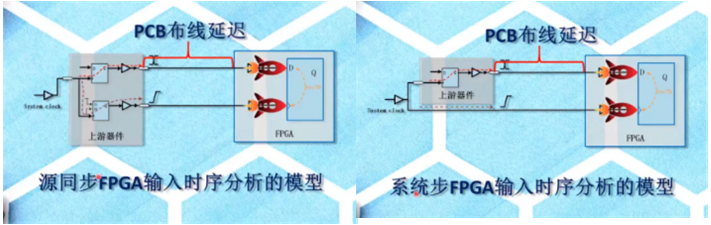

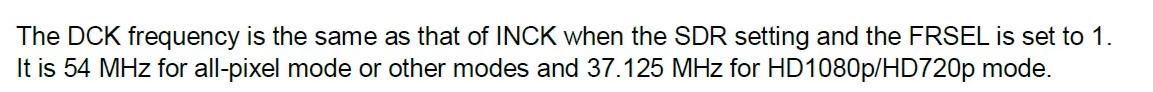

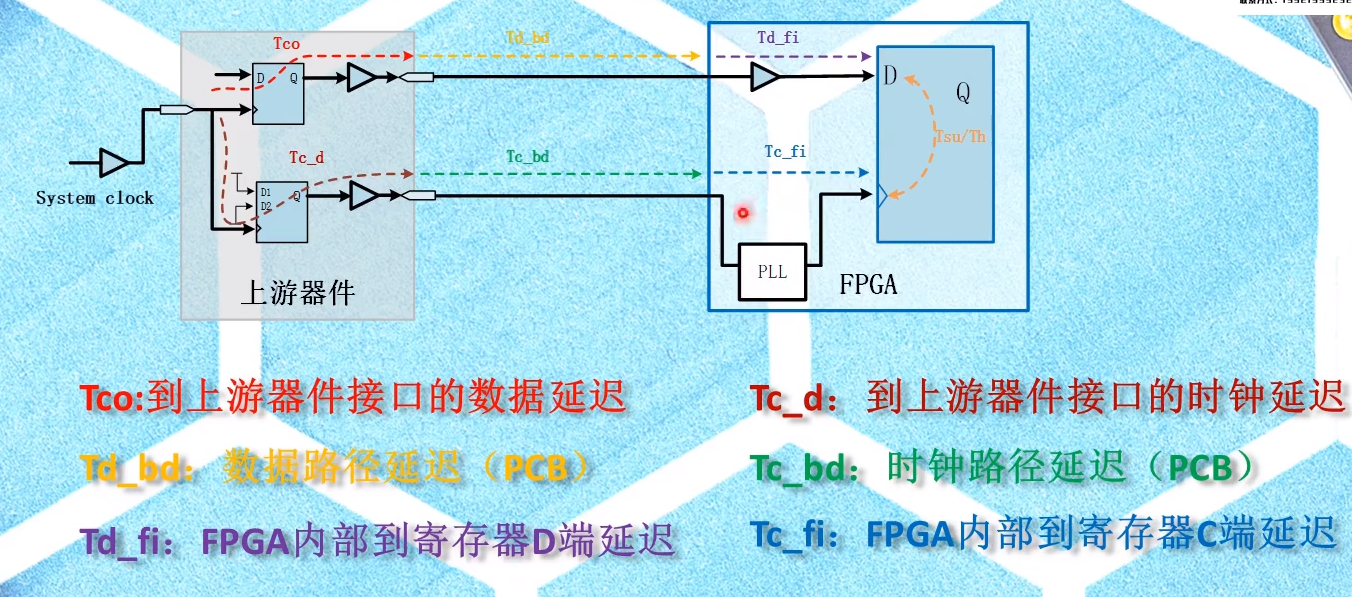

6.3.1 基本模型

- 源同步是由上游器件提供同步时钟和同步数据给下游器件(FPGA)

(逐渐被高速的串行总线 PCIE 、SATA 、USB3.0,其传输中只有串行的数据,没有了同步的时钟)

eg.千兆以太网PHY、中低速的AD/DA、SPI

- 系统同步是由PCB板的晶振源,时钟源分别给上游器件和下游器件(FPGA)

(随着高速传输,很少)

Q:对于FPGA分频产生的时钟源,该如何理解?

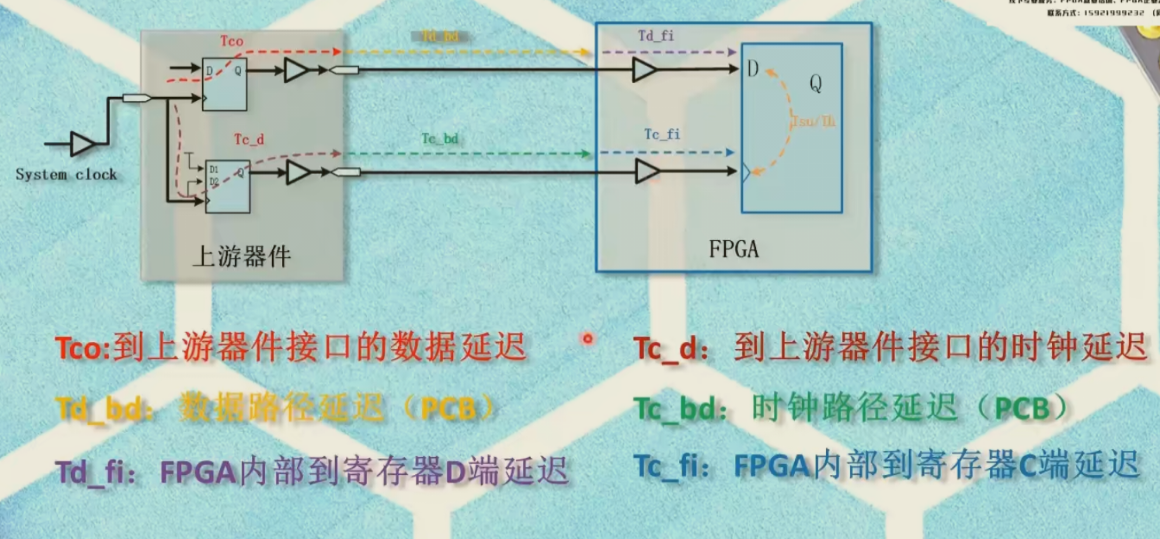

6.3.2 IO时序输入延时

高速数据线等长的原因

多条数据线 延时 存在最大最小值(线长、线宽、阻值等因素)

--延时最大时,分析建立时间裕量

--延时最小时,分析保持时间裕量

这里没考虑时钟线也存在最大最小值的情况(温度、生产工艺),即认为Tc_bd固定

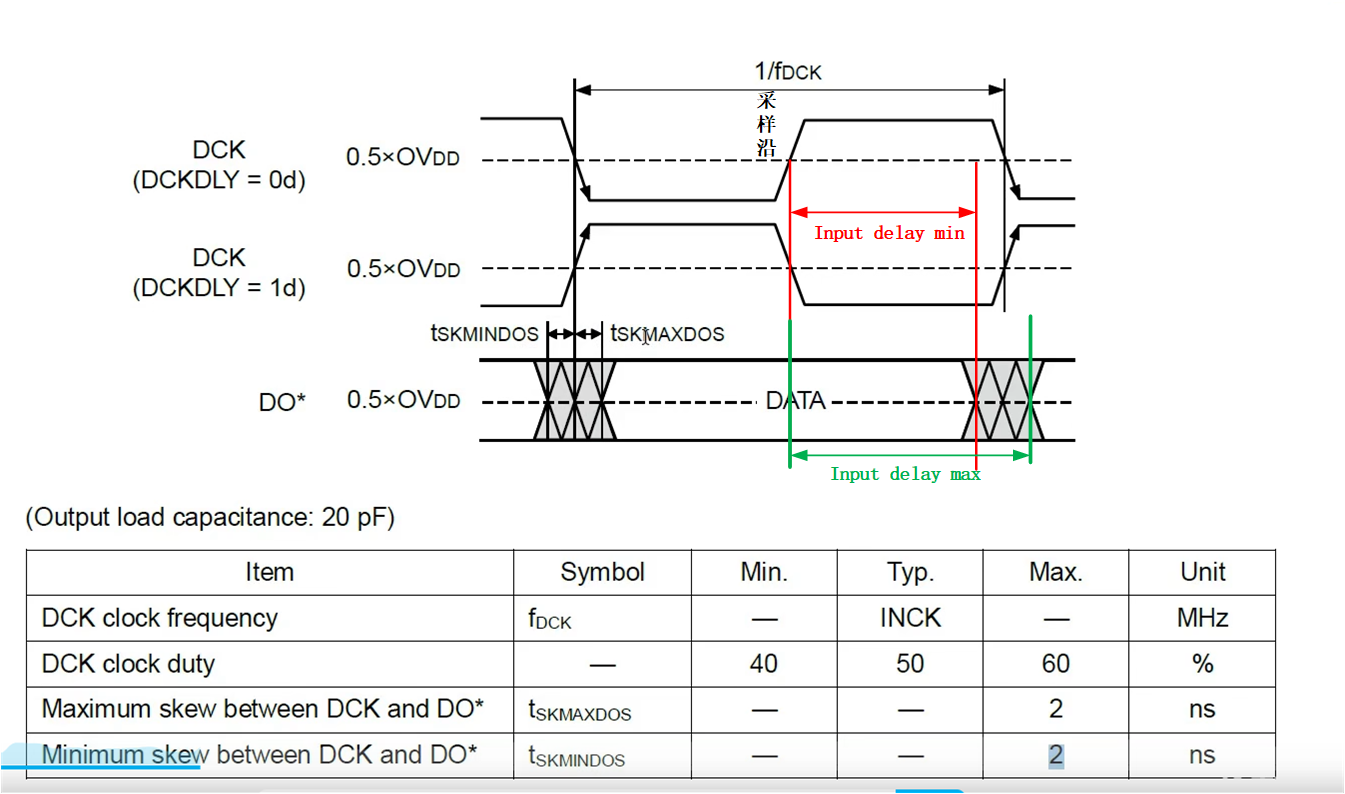

6.3.3 实际分析-中心对齐

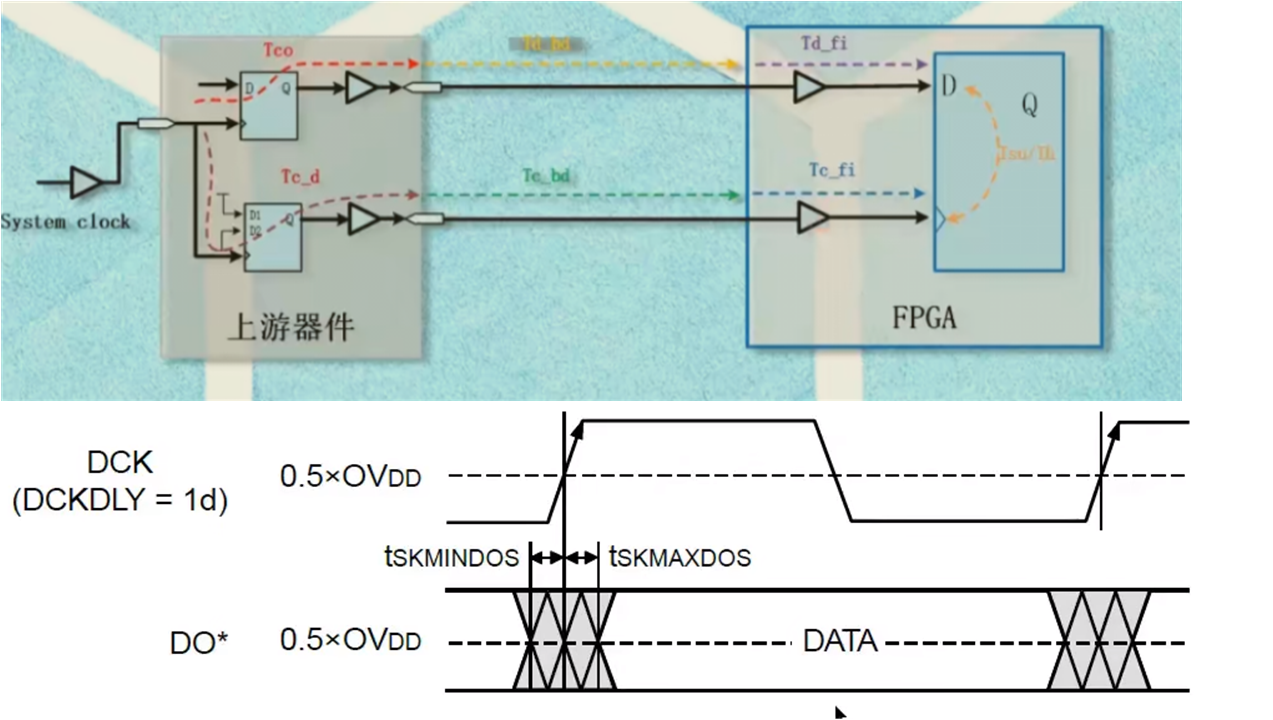

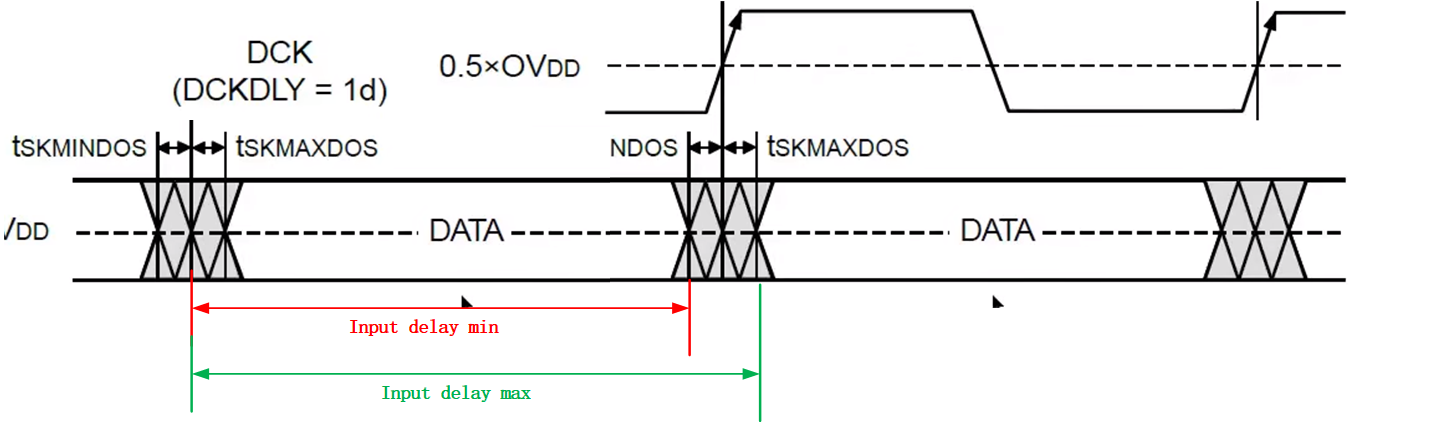

Input delay 描述的是发射数据的上升沿到数据起始位置的延时

阅读芯片的datasheet,找到时钟和数据输出的关系(相位)

中心对齐的Input delay 发射的时候是上升沿发射的,但是传输到目的寄存器过程中,由于延时时钟比数据早半个周期到;

整体为上升沿采样

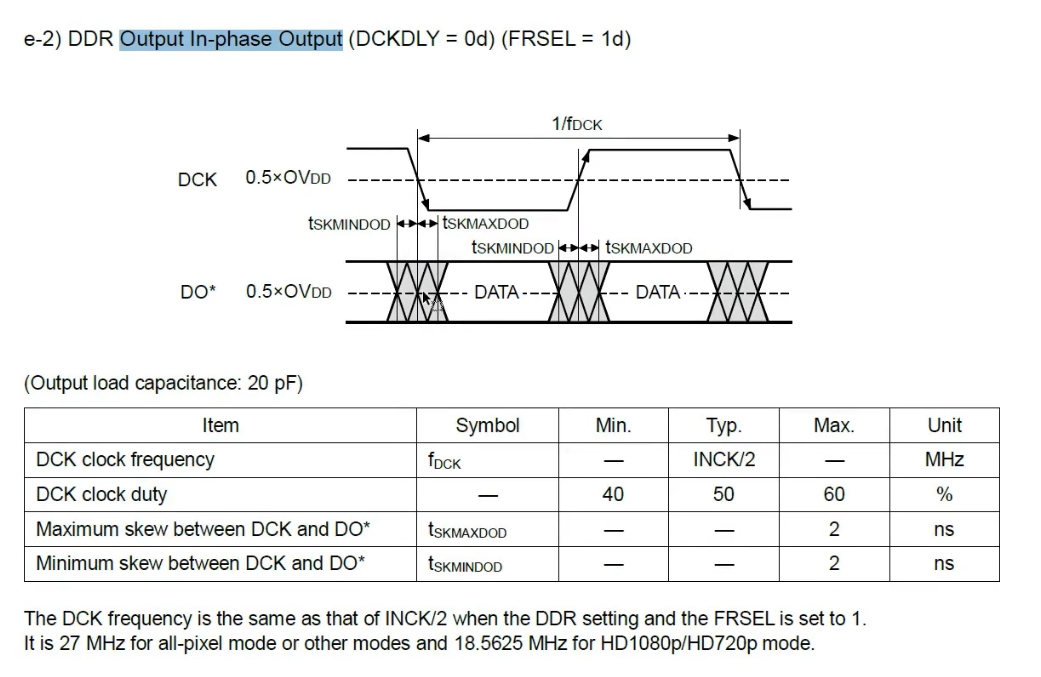

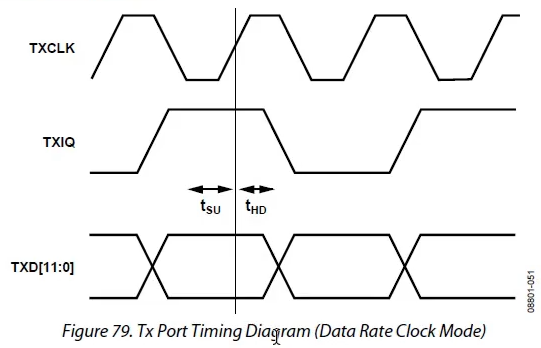

DCKDLY=0d 中心对齐(数据中心采样)

DCKDLY=1d 边沿对齐 (时钟和数据相同边沿变化)

对应不同的约束

DCKDLY=0d 中心对齐

input delay min = (1/54 MHZ) /2-

input delay max= (1/54 MHZ) /2 +

讨论PCB的延时,时钟延时和数据的延时之差是多少

一般情况下,在布线时做等延时约束

- 在板卡已经做了等延时约束的情况下,认为从芯片到FPGA的时钟和数据延时是一致的,就是芯片的输出状态

- 倘若发现时钟和数据的延时不一致,则可进一步联系PCB工程师,索要具体延时(介电常数等等可具体计算)

进行以 FPGA为中心的Input dealy 分析

Fast Process Corner:低温高压(电压,走线,延迟最佳)

slow Process Corner : 高温低压(时序相应会变差)

6.3.4 实际分析-边沿对齐

6.3.4.1 问题

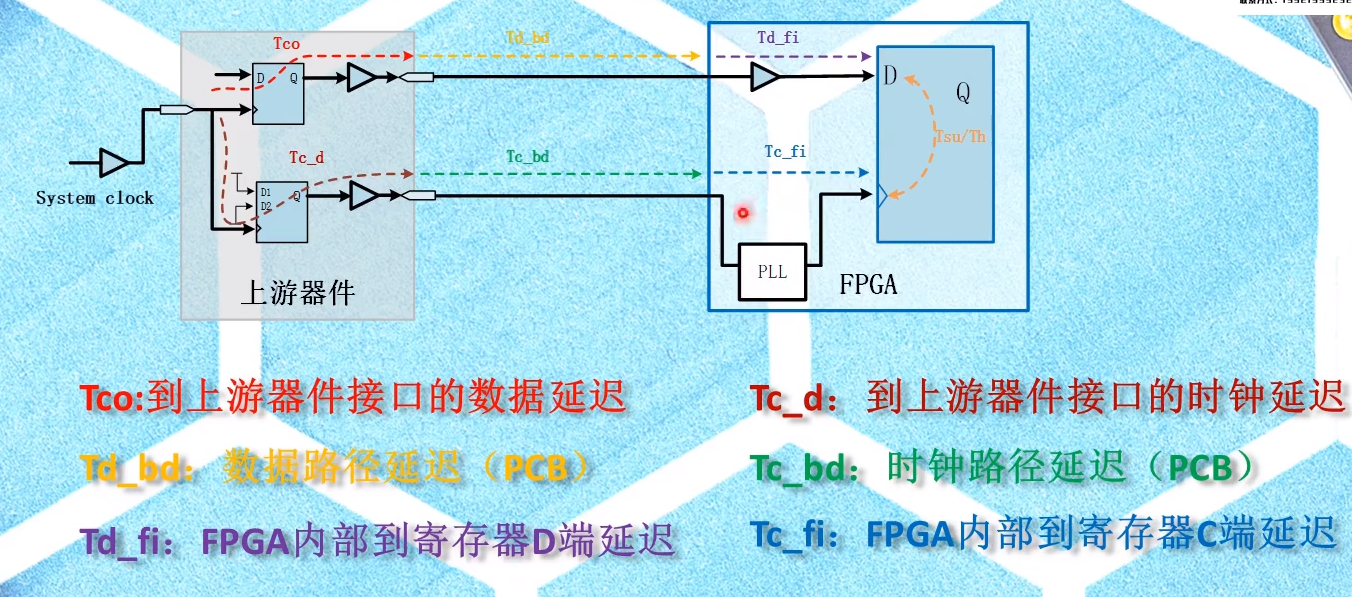

考虑 实际的 Td_fi Tc_fi 不确定,可以通过边沿对齐,观察一下FPGA内部具体的情况

6.3.4.2 结果

直接借用 6.3.3的结果,修改 max min 为 2/-2 ,

- (不进行重新综合,布线,使用之前的网表进行分析)报错 建立时间满足,保持时间不满足(时钟延迟太大 or 数据延迟太小)

- 进行重新综合,均满足 xilinx 自动优化?

6.3.4.3 修改1-不可行

对于不满足,这里考虑利用下一个边沿(增加数据延迟,已经脱离了边沿对齐)

使用上一个时钟周期,采这个时钟周期的数

max = 时钟周期+2

min= 时钟周期-2

则建立时间不满足,而保持时间不满足(时钟采样沿时,数据还没有到达)

6.3.4.4 修改2-硬件上进行修改

通过添加一个PLL

- 可以移相

- 可以对chip管脚到PLL的时钟进行补偿

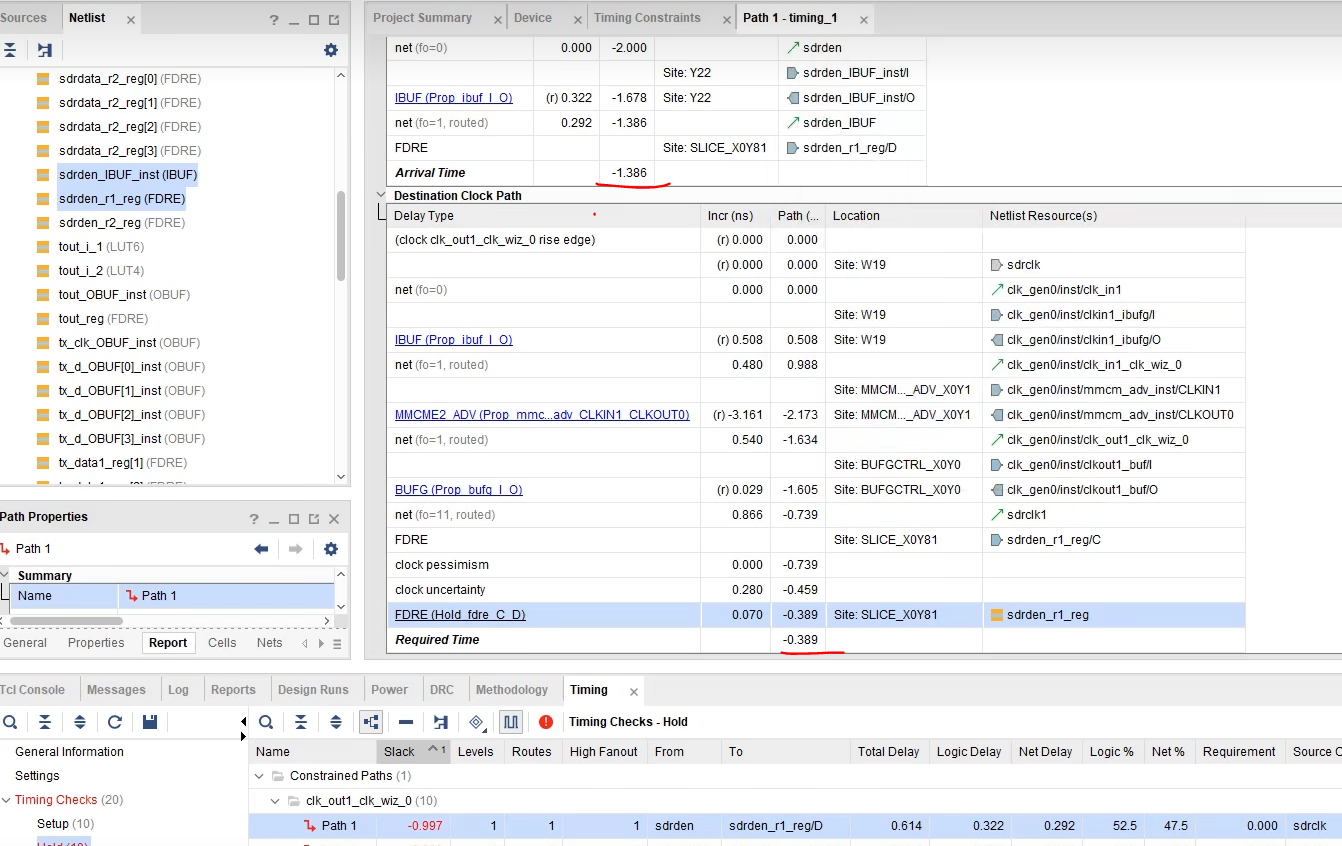

分析本数据的保持时间,使用数据实际结束时间:(-1.386+T)-数据要求结束时间(-0.389+T),

需要让数据继续向左(负值)移动,使得上升采样沿可以不遗漏地采样到所有的数据,这里调整PLL

修改参数后,重新生成网表

时钟信号走全局时钟,一般统一使用上升沿触发,且节省CLB资源

不可以对使用信号取反,取反的网表上会引入额外的反相器?

- 取反是CMOS第二中时序控制方式

PLL数量有限

Xilinx中可以直接使用 IDelay原语?

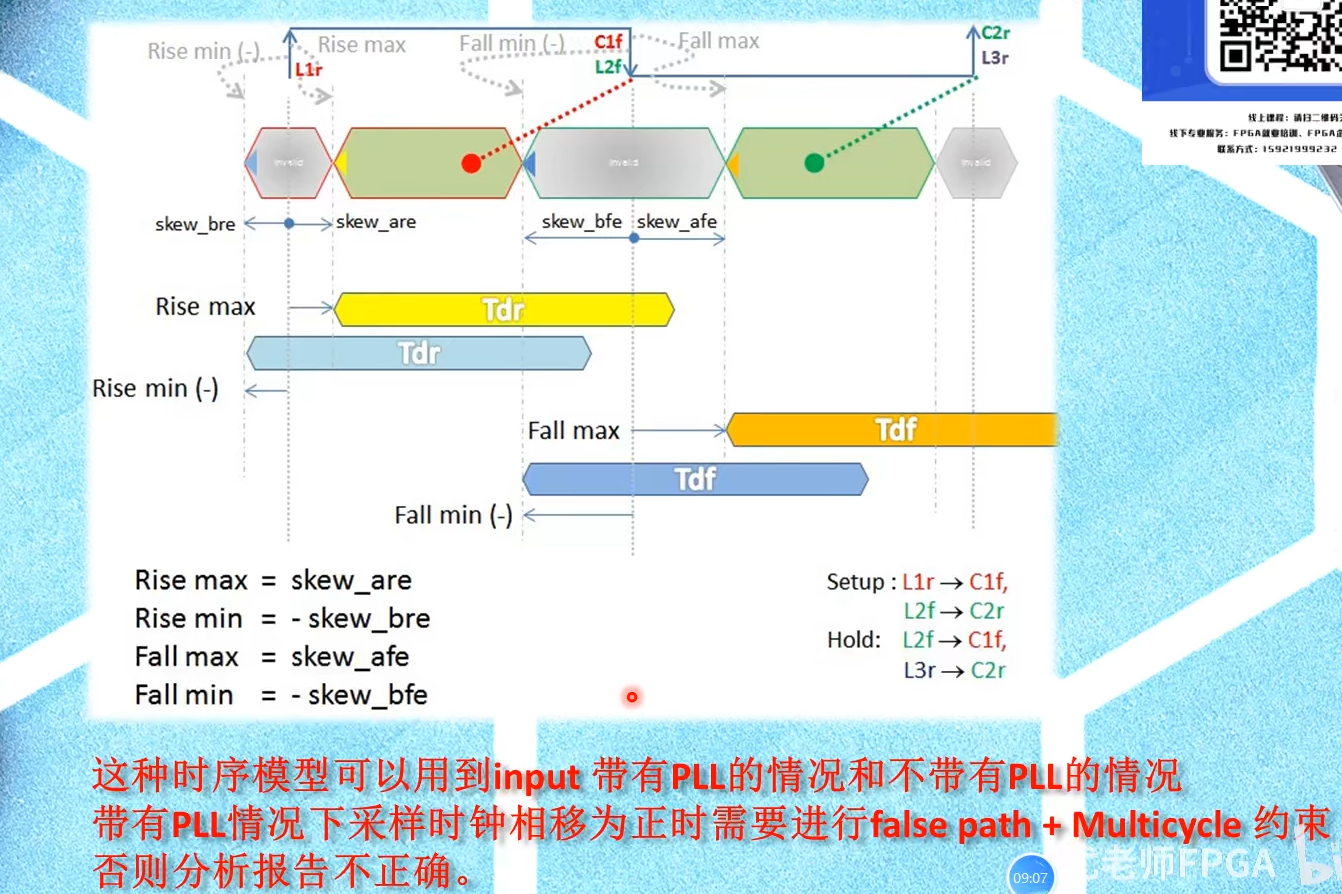

6.3.5 边缘对齐 不同时序模型对比

L1r 发射沿

C1r 采样沿

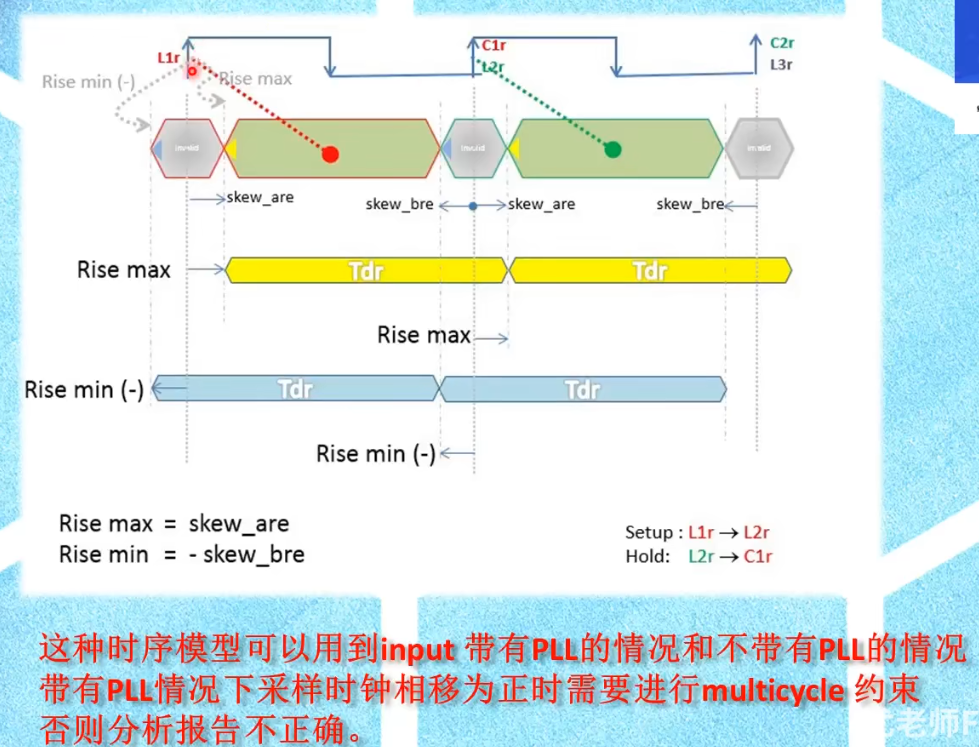

对于有PLL的情况:

1.利用PLL,负向移动即可

2.若是选择PLL 相移为正

建立时间不满足,分析点错误,应该使用第二个上升沿分析建立时间

set是本来是分析一个周期,hold是分析结束到结束

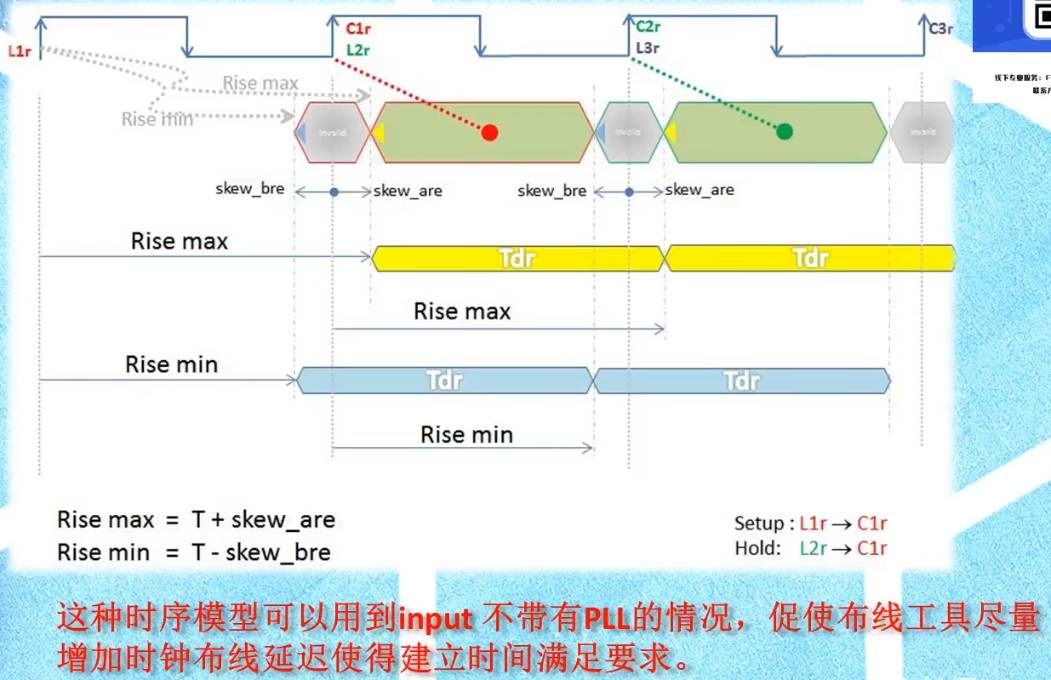

对于没有PLL的情况:

(布线时)时钟往前

数据无法比时钟的延时更长一些,导致违例:

增加数据延时 (只修改约束为 max=2 /min= -2)

布线工具为了尽可能的满足约束,软件自动把数据线变长

6.4 DDR-Direct 输入延迟约束

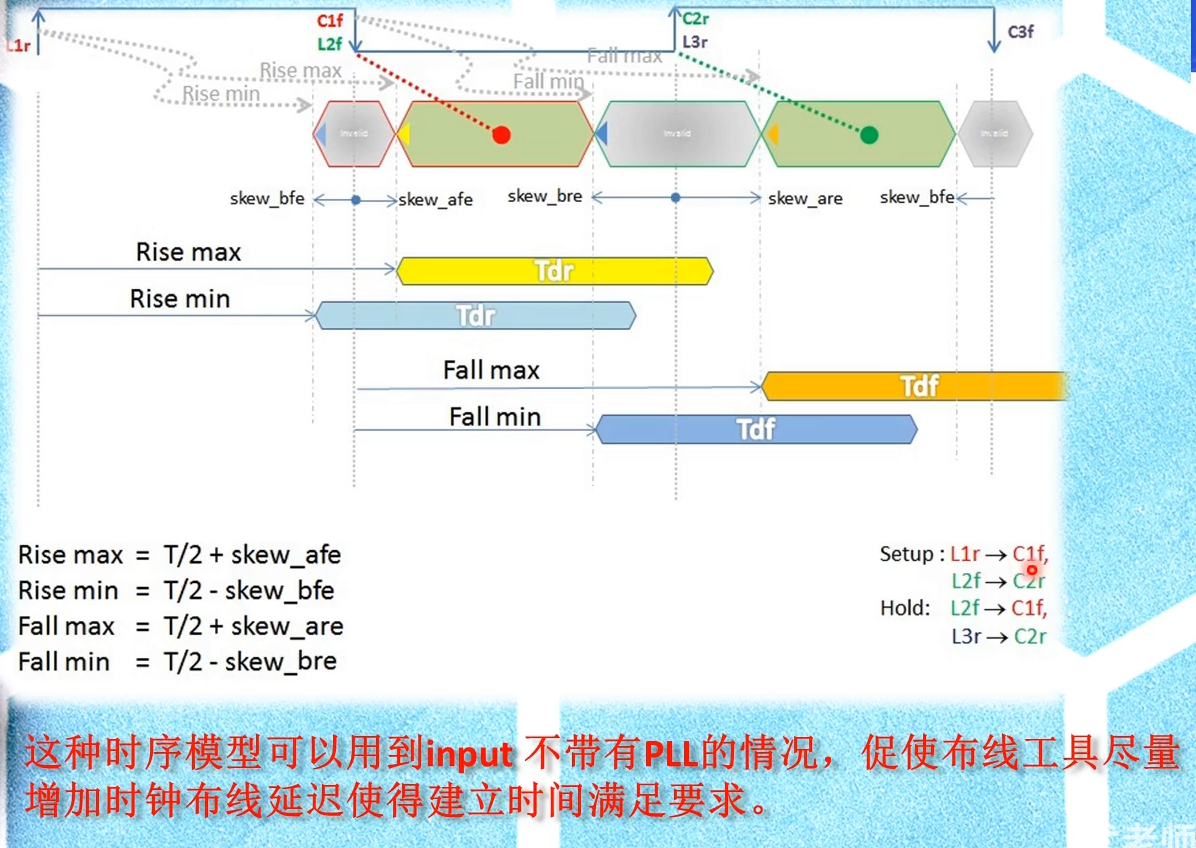

源同步-双沿

千兆网PHY和FPGA交互 ; DDR的DRAM 双边沿采样 、AGC 、 CMOS芯片、LVDS

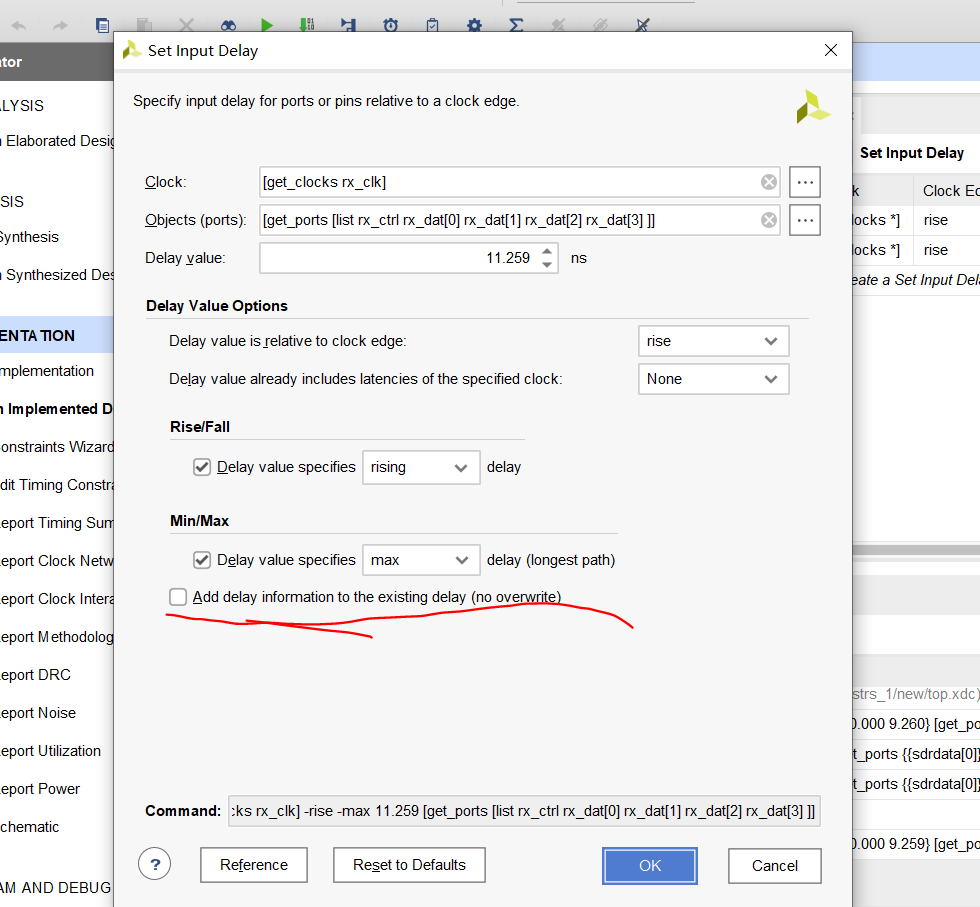

上升沿、下降沿的有效情况是不一致的

认为 下降沿要采样的数据是由上一个上升沿发送而来的,

认为 上升沿要采样的数据是由上一个下降沿发送而来的。

对于同一条链路,既要约束上升沿,也要约束下降沿时,需要勾选下图,否则会覆盖掉前者。

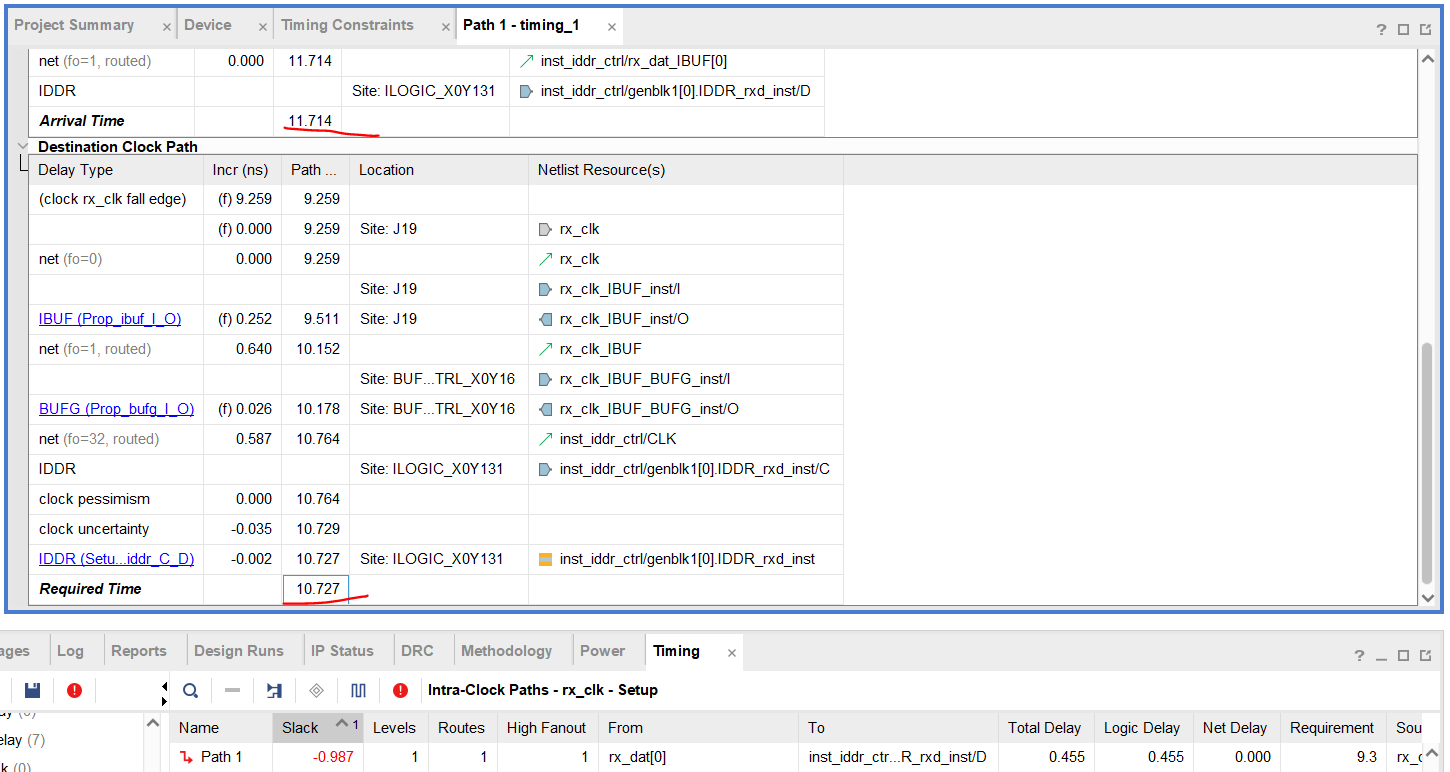

做对了正确的约束,得到了正确的报告

发现:建立时间不满足,需要增加时钟延时

vivado设计优化参数

改动代码

进一步,通过IDelay原语增加延时

完成时序约束

6.5 DDR-PLL/MMCM 输入延迟约束

B站弹幕:【-2,2】约束比上一节的约束好,布线工具可以增加数据线延时来保证收敛

PLL 负向相移

对于两个上升沿之间是没有分析的必要的

可以通过设置 false path 进行过滤

时序收敛

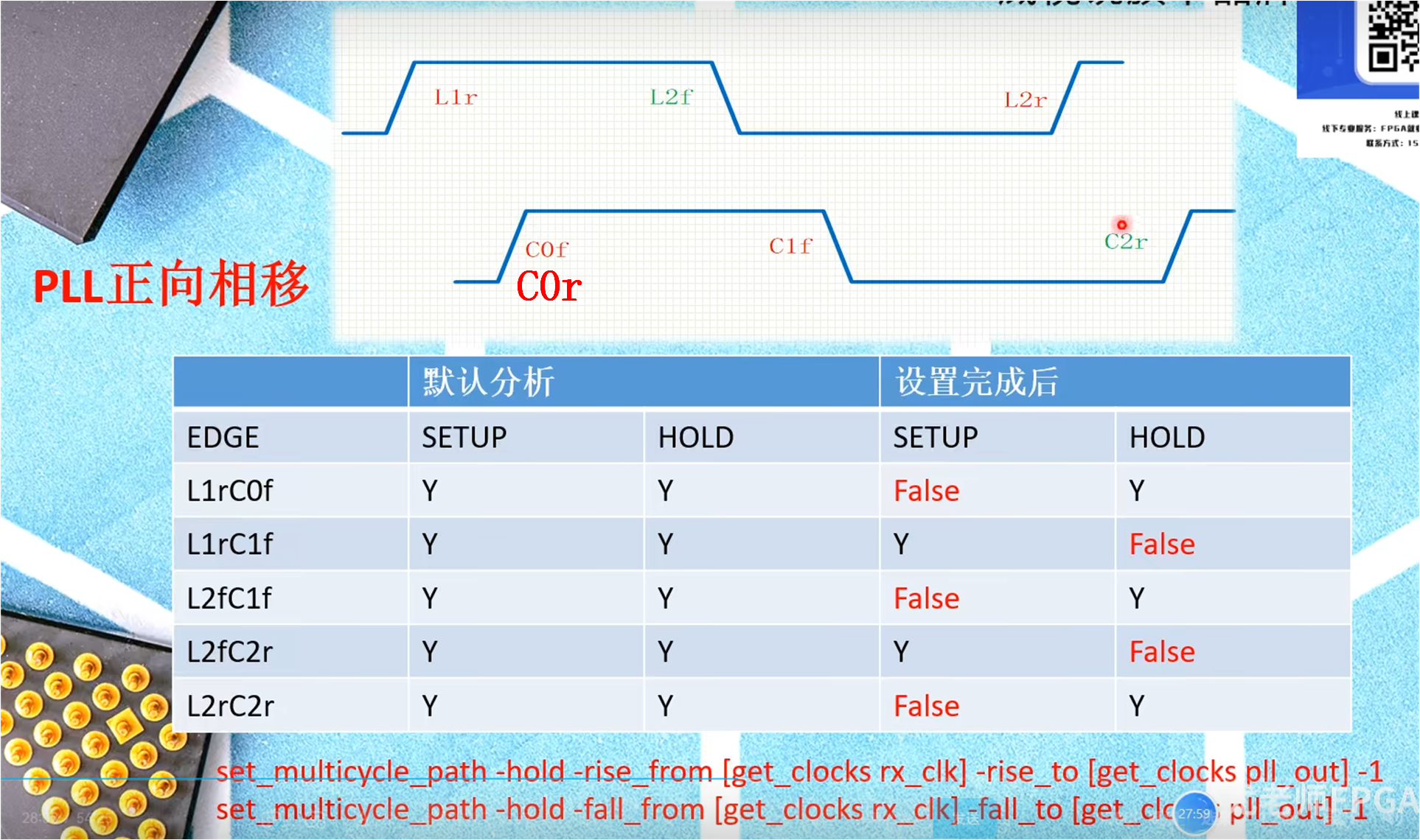

PLL 正向相移 30

set false path

set_false_path -setup -rise_from [get_clocks rx_clk] -rise_to [get_clocks -of_objects [get_pins clk_gen0/inst/mmcm_adv_inst/CLKOUT0]]

set_false_path -setup -fall_from [get_clocks rx_clk] -fall_to [get_clocks -of_objects [get_pins clk_gen0/inst/mmcm_adv_inst/CLKOUT0]]

set_false_path -hold -reset_path -rise_from [get_clocks rx_clk] -fall_to [get_clocks -of_objects [get_pins clk_gen0/inst/mmcm_adv_inst/CLKOUT0]]

set_false_path -hold -fall_from [get_clocks rx_clk] -rise_to [get_clocks -of_objects [get_pins clk_gen0/inst/mmcm_adv_inst/CLKOUT0]]

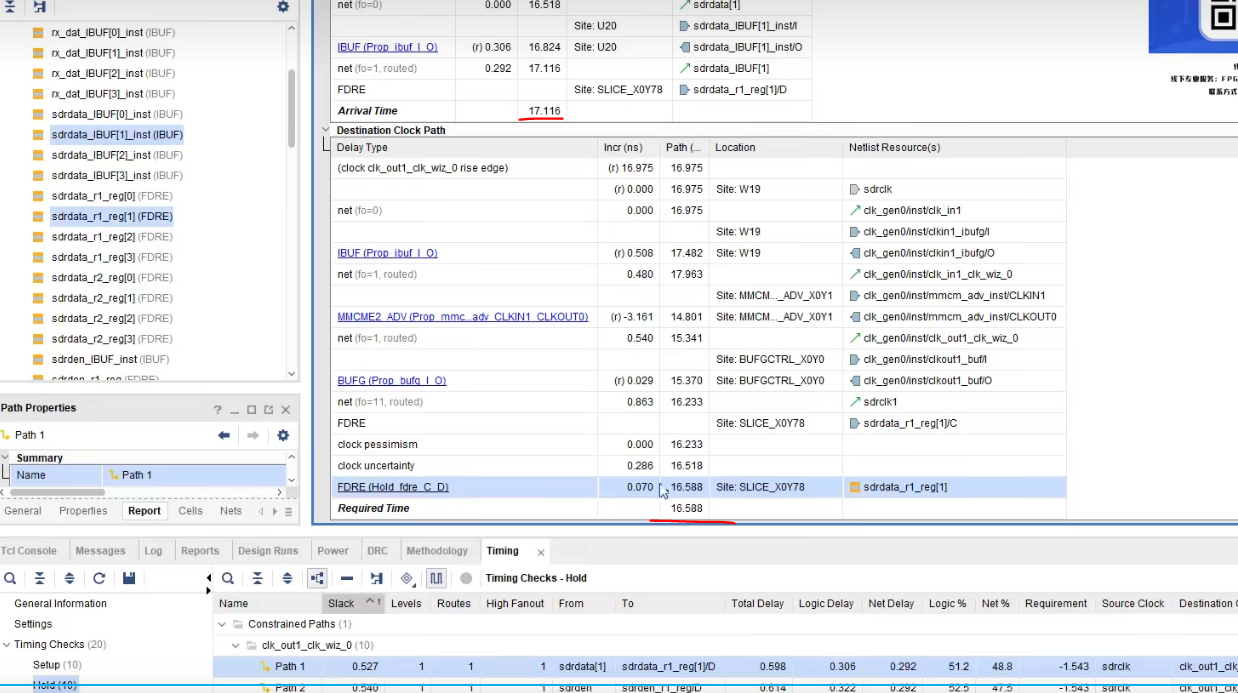

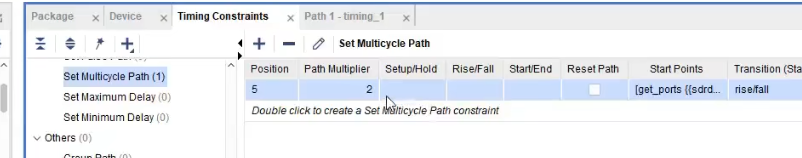

存在L1r - C0r, 需要设置multicycle

错误的路径是L1r到C2r,hold设置为正数时默认右移源时钟或者左移目的时钟,所以将hold值设为-1,也就是将源时钟左移一个时钟周期,路径也就变为L1r到C0r

set_multicycle_path -hold -rise_from [get_clocks rx_clk] -rise_to [get_clocks -of_objects [get_pins clk_gen0/inst/mmcm_adv_inst/CLKOUT0]] -1

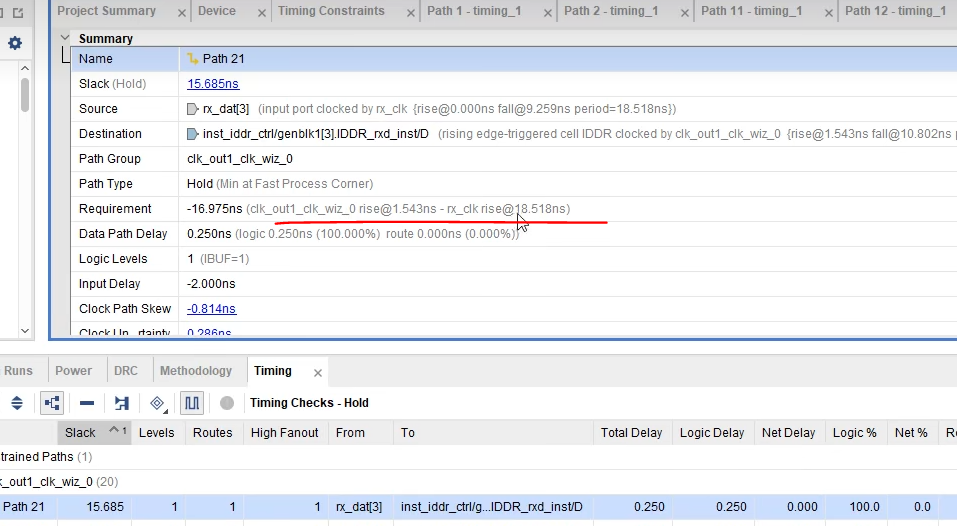

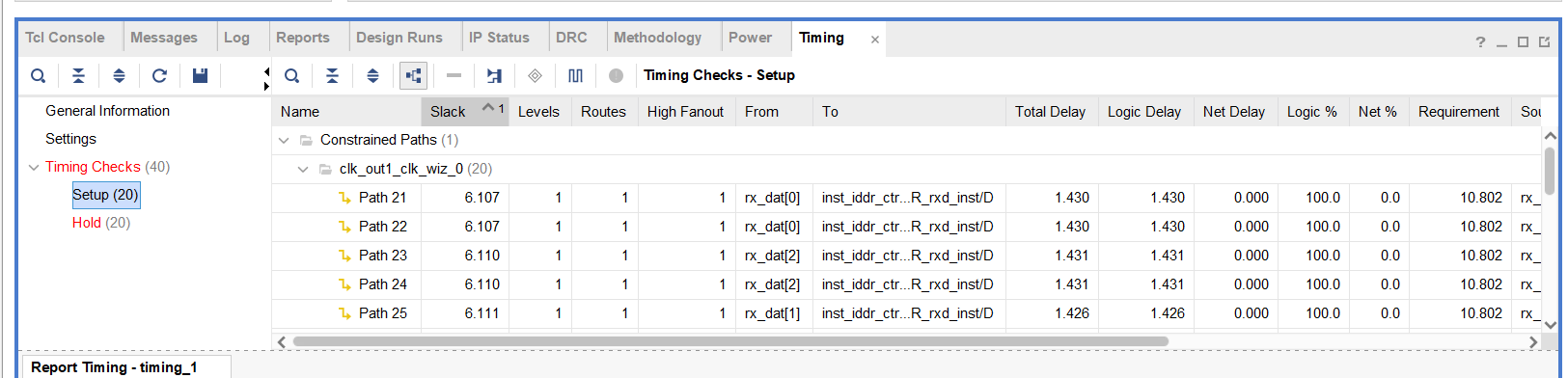

set_multicycle_path -hold -fall_from [get_clocks rx_clk] -fall_to [get_clocks -of_objects [get_pins clk_gen0/inst/mmcm_adv_inst/CLKOUT0]] -1需要得到正确的时序报告,软件对于优化时序的能力不强,不会自动插入延迟

滤除无关路径后,进一步考虑如何优化

下一个问题,如何时序收敛?

我们由上述时序报告可以看出,建立时间裕量大,保持时间裕量为负,即需要通过PLL设置负向移动,调整时钟完成!

6.6 输出延迟 约束

ASIC后端还需要专门进行布局布线,FPGA则布局布线已经固定

6.6.1 基本理论

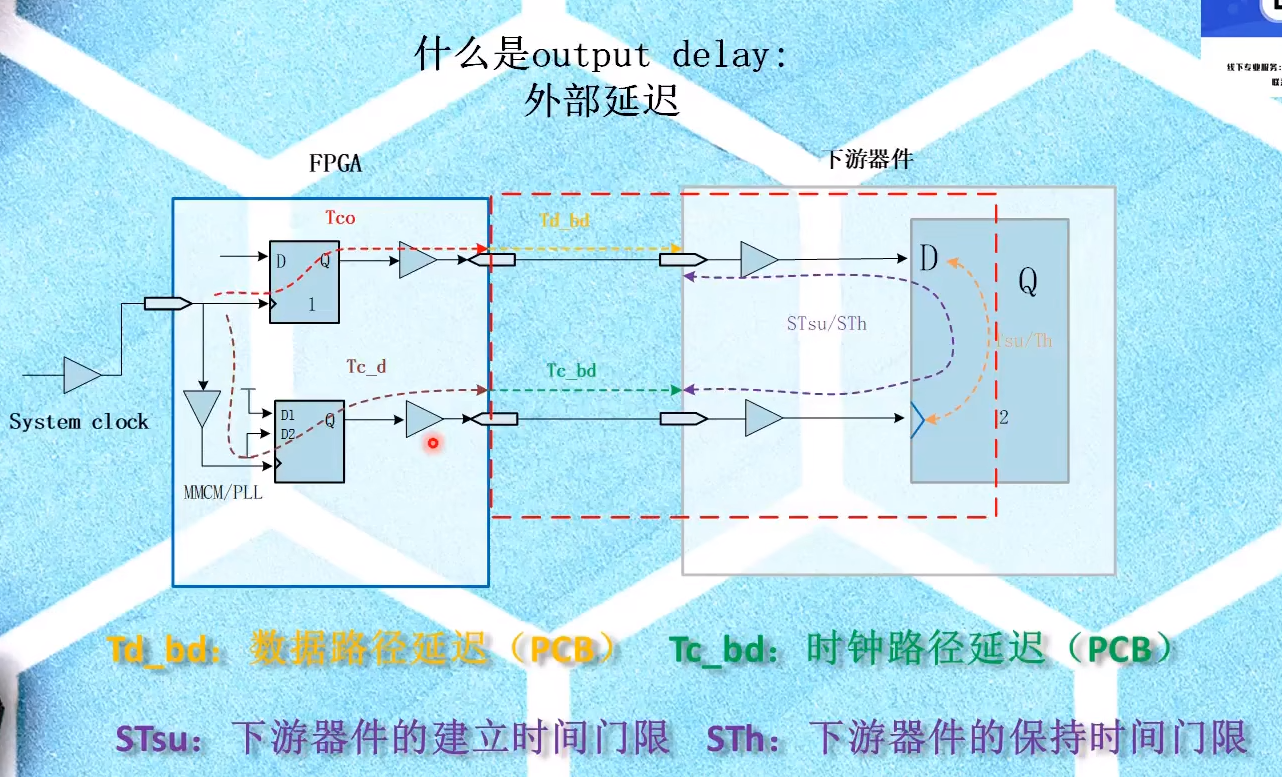

下游器件可能是模糊的,可能只有对输入时钟和数据的对齐方式,以及skew偏差进行的要求说明。

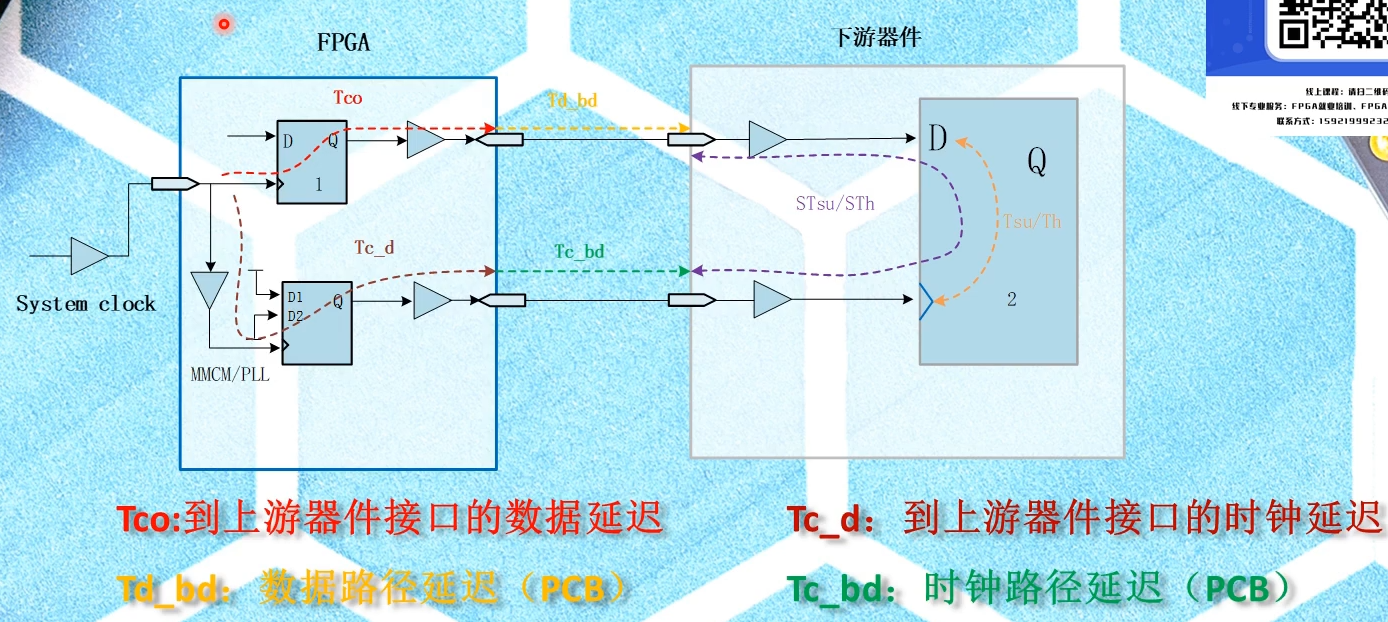

Input delay 是参考 到达FPGA芯片位置,发射沿和数据到达时刻的关系

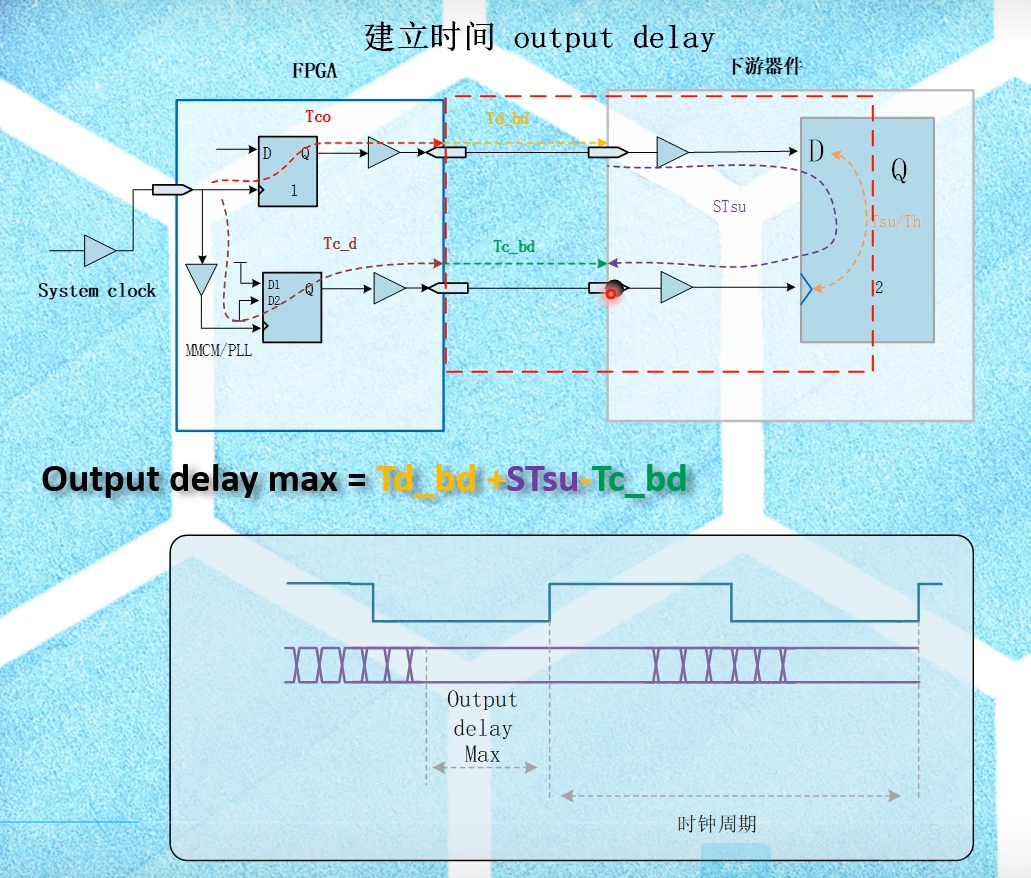

Ouput delay 是参考 到达下游芯片位置,目的采样沿和数据到达时刻的关系

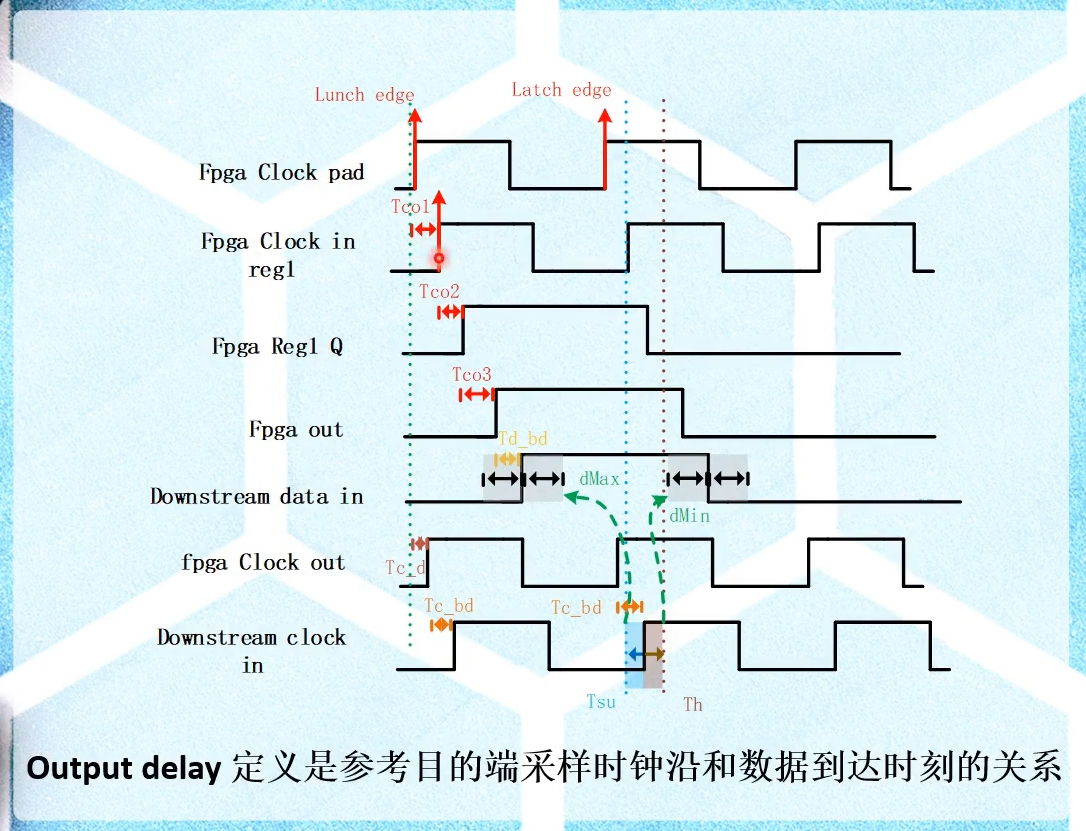

dMax 建立时间裕量

dMin 保持时间裕量

output delay ? 【Tsu-dMax,Th+dMin】 适当宽松

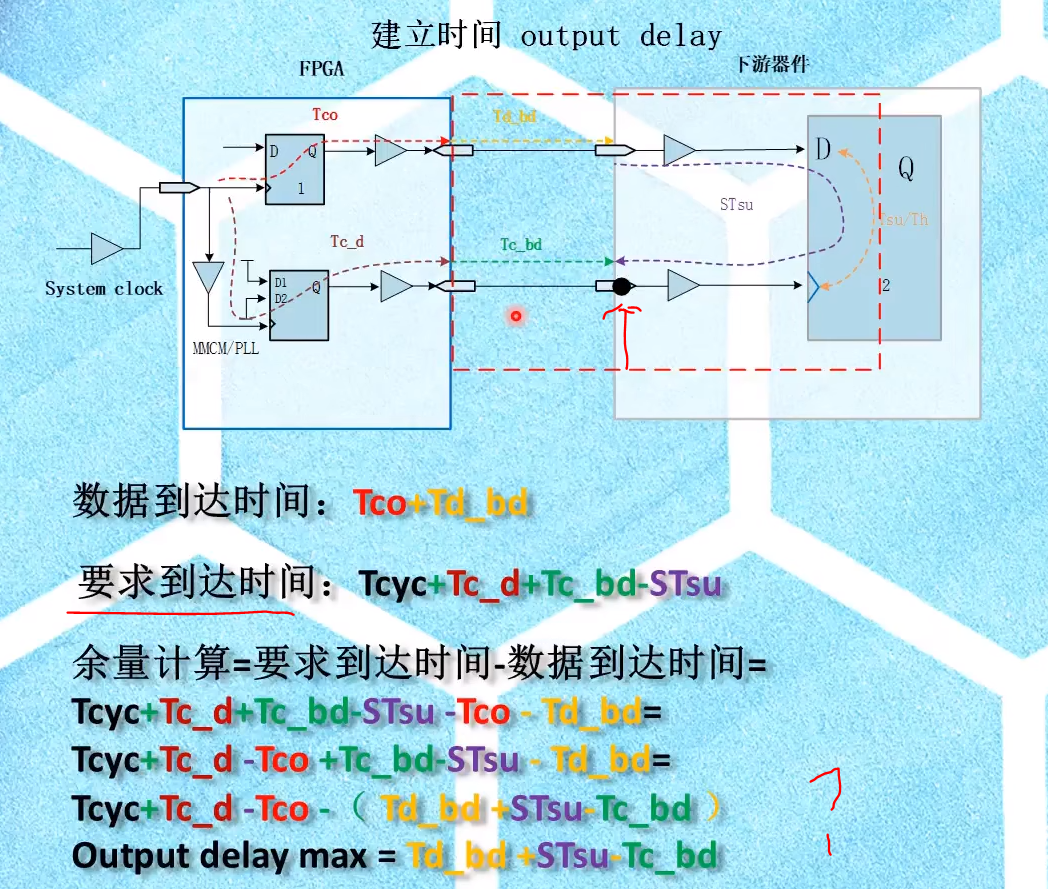

6.6.2 建立时间-分析

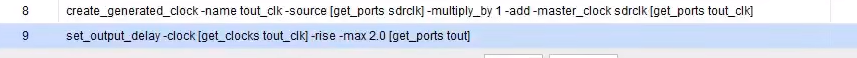

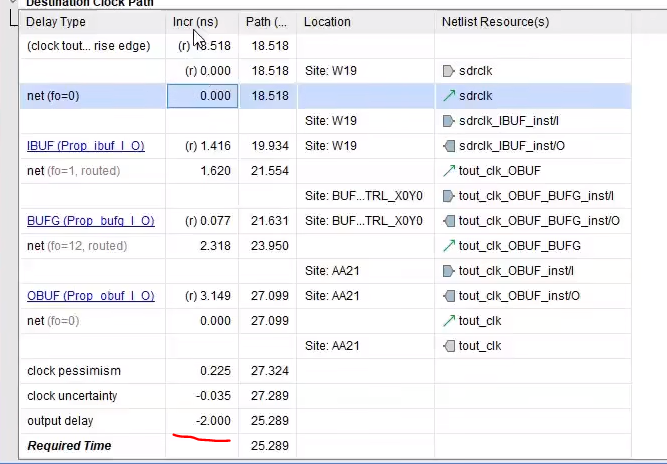

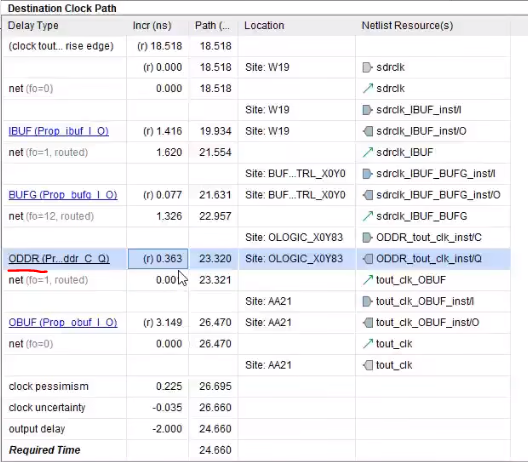

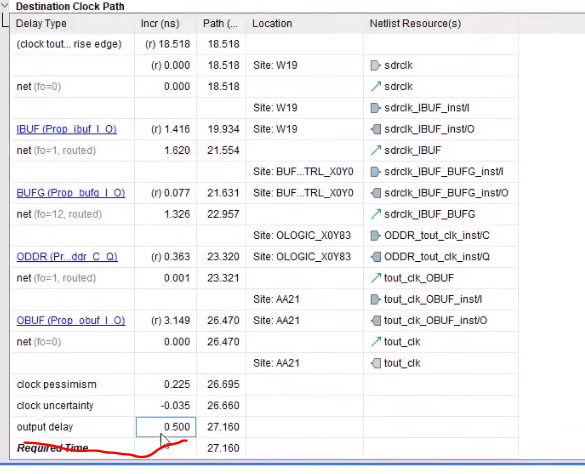

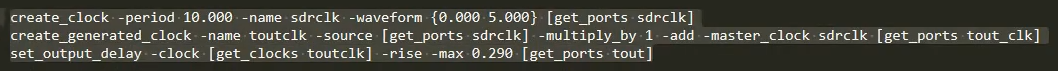

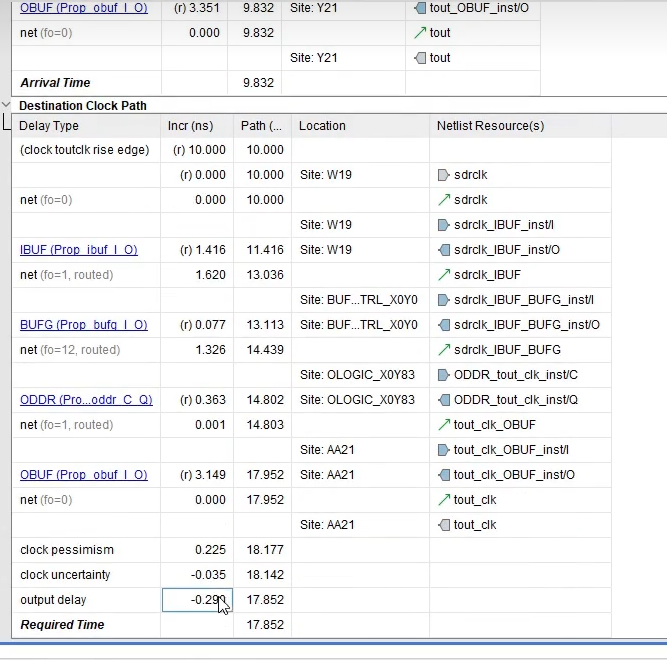

构建源同步模型(生成时钟),并添加输出延时(时钟路径上减去了Output delay max,下面设置为2)

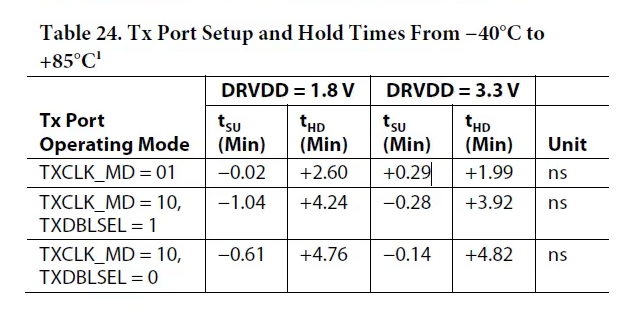

如果PCB布线等长的话(Td_bd=Tc_bd),output_delay=下游器件的建立时间门限 sTsu

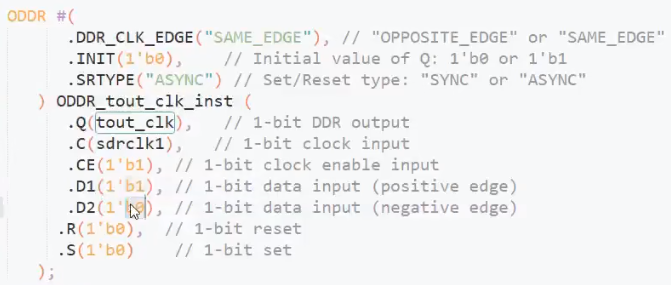

说法:输出的时钟最好经过ODDR,那么经过ODDR如何进行约束?

利用ODDR,后续到达OBUF的路径直接使用专门时钟路径(比较好控制的时钟路径)

Q:倘若Td_bd=3ns,Tc_bd=4ns,sTsu=0.5 ns,则 Output delay max 应该如何约束?

Output delay max = -0.5

和vivado 分析工具一致

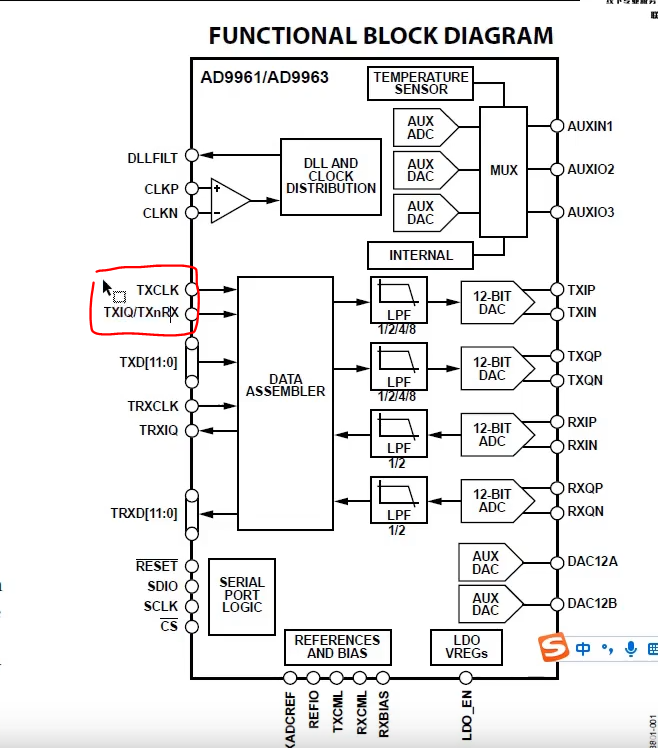

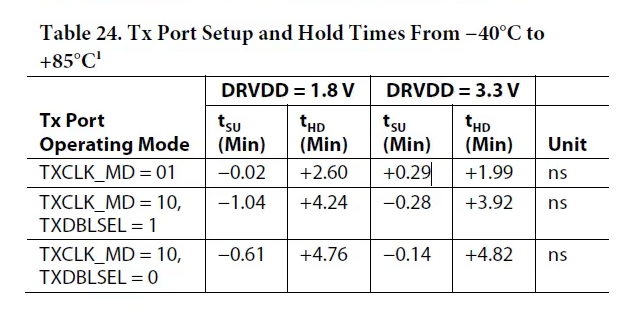

6.6.3 建立时间-结合AD

AD9963

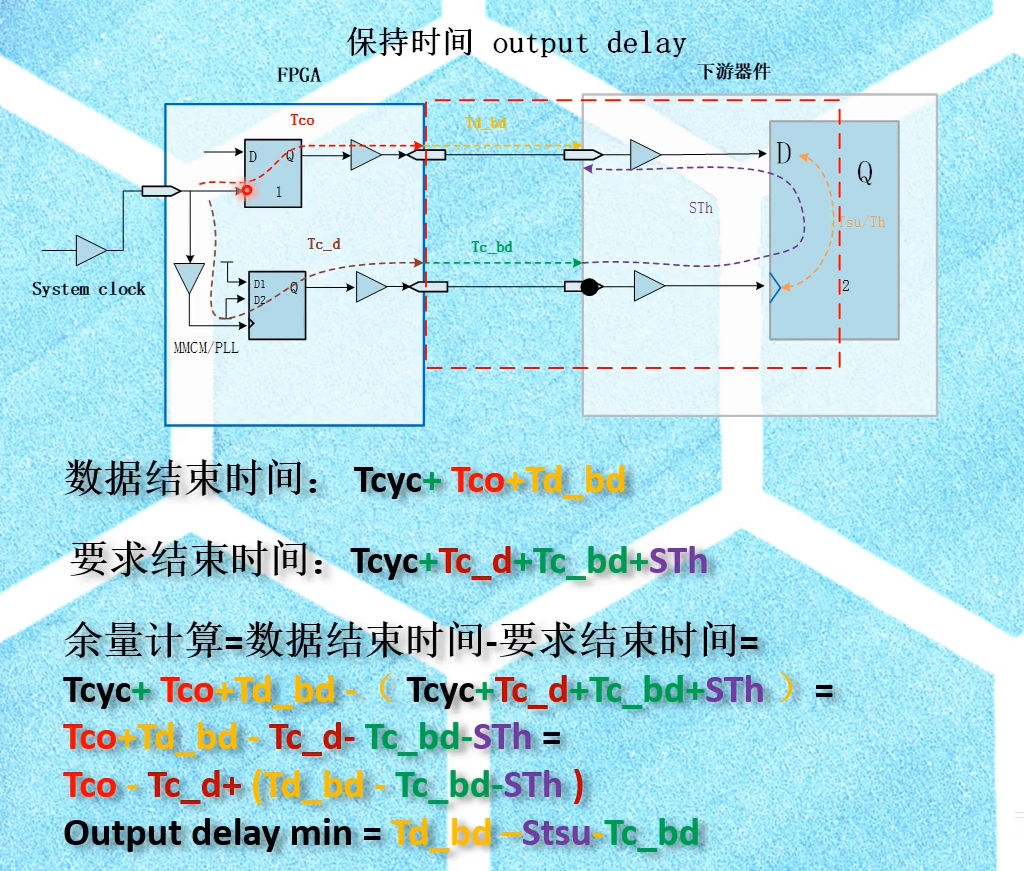

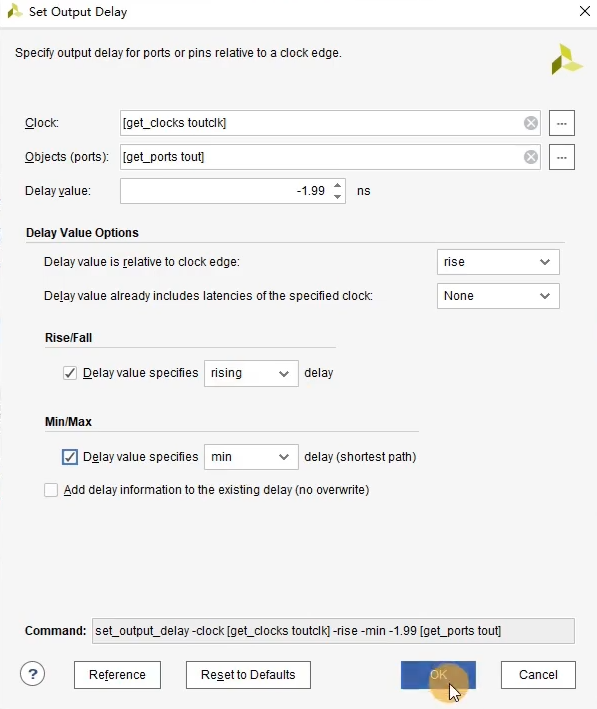

6.6.4 保持时间

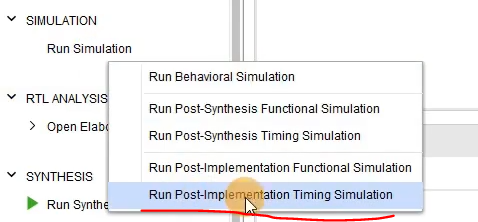

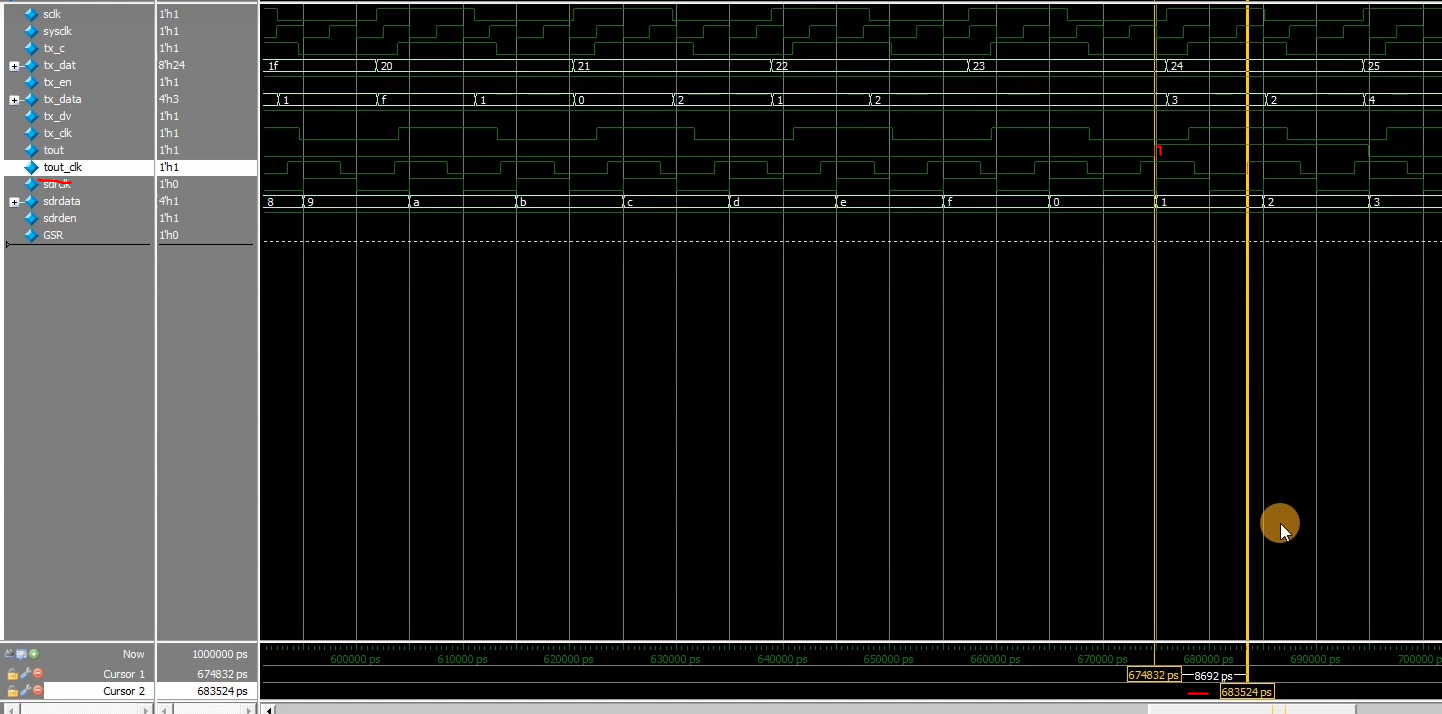

通过仿真观察约束的效果 (后仿真,具备了延时信息)

测试1

设置 output delay max =0.79 ns

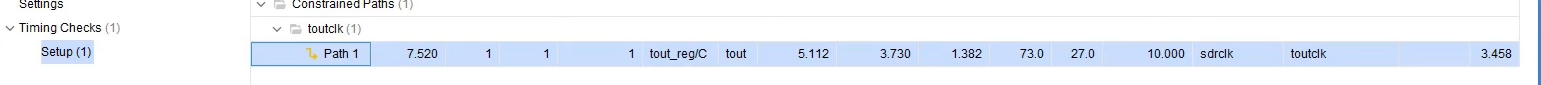

建立时间裕量:7.52 ns

建立时间为8.692ns(和时序分析值应存在同一水平,具体受模型,参数的影响)

后仿真 建立时间裕量 8.692 - 0.79 = 7.902 ns

测试2

设置 output delay max =2.79 ns

时序报告里 setup slack = 5.520 ns

布局布线后,再次后仿真: 仍为 8.692 ns

测试3

最终填入约束的值 是 +1.99? 还是 -1.99?

设置 output delay max =0.79 ns

设置 output delay min = -1.99ns

在采样沿 左边为正 ,在采样沿右边为负

叠加到了时钟延时上,Stsu 和 Tc_bd 同向

观察增加hold time约束,后仿真结果

当前时钟周期为10ns ,建立时间为 8.692 ns ,建立时间裕量为 8.692-0.79 = 7.902ns

保持时间为 1.99ns, 保持时间裕量为 1.99 ns + 0.371 ns

结果:缩小建立时间,增大保持时间(由于增加hold time 约束)

6.7 小总结

- 做约束是限定条件,自动布线无法实现时,需要手动调整;或者约束过于苛刻

- vivado工具依照理论分析进行布线

- IO约束,FPGA内部约束的基本约束,规则,思想有了一定的认识

- 更进一步,需要在细节上,分析工具行为和基本原理是否正确

七、时序约束策略

参考链接-微信文章 数字ICer-时序约束策略

IO约束

管脚约束

指定管脚的位置

PACKAGE_PIN和管脚对应的电平标准IOSTANDARD两个属性的值set_property PACKAGE_PIN AD8 [get_ports srio_rxp0]延迟约束 (input/output delay)

create_clock -name sysclk -period 10 [get_ports clkin] set_input_delay 2 -max -clock sysclk [get_ports Datain] set_input_delay 1 -min -clock sysclk [get_ports Datain]

时钟周期约束

- Create_clock

- create_generated_clock 衍生时钟

- set_clock_groups时钟分组

- 虚拟时钟

- 外部IO的参考时钟并不是设计中的时钟

- FPGA I/O路径参考时钟来源于内部衍生时钟,但与主时钟的频率关系并不是整数倍

- 针对I/O指定不同的

jitter和latency

- 最大最小延迟约束

- 输入管脚的信号经过组合逻辑后直接输出到管脚

- 异步电路之间的最大最小

多周期约束

数据被发起后,由于路径过长或者逻辑延迟过长要经过多个时钟周期才能到达捕获寄存器;又或者在数据发起的几个周期后,后续逻辑才能使用。这时如果按照单周期路径进行时序检查,就会报出时序违规。因此就需要多周期路径约束。

伪路径

伪路径指的是该路径存在,但该路径的电路功能不会发生或者

无须时序约束XDC约束优先级

时序例外的优先级从高到低为:

- Clock Groups (

set_clock_groups) - False Path (

set_false_path) - Maximum Delay Path (

set_max_delay) and Minimum Delay Path (set_min_delay) - Multicycle Paths (

set_multicycle_path)

- Clock Groups (