09.理解AXI4 总线

09.理解AXI4 总线

参阅 知乎专栏:https://zhuanlan.zhihu.com/p/44766356

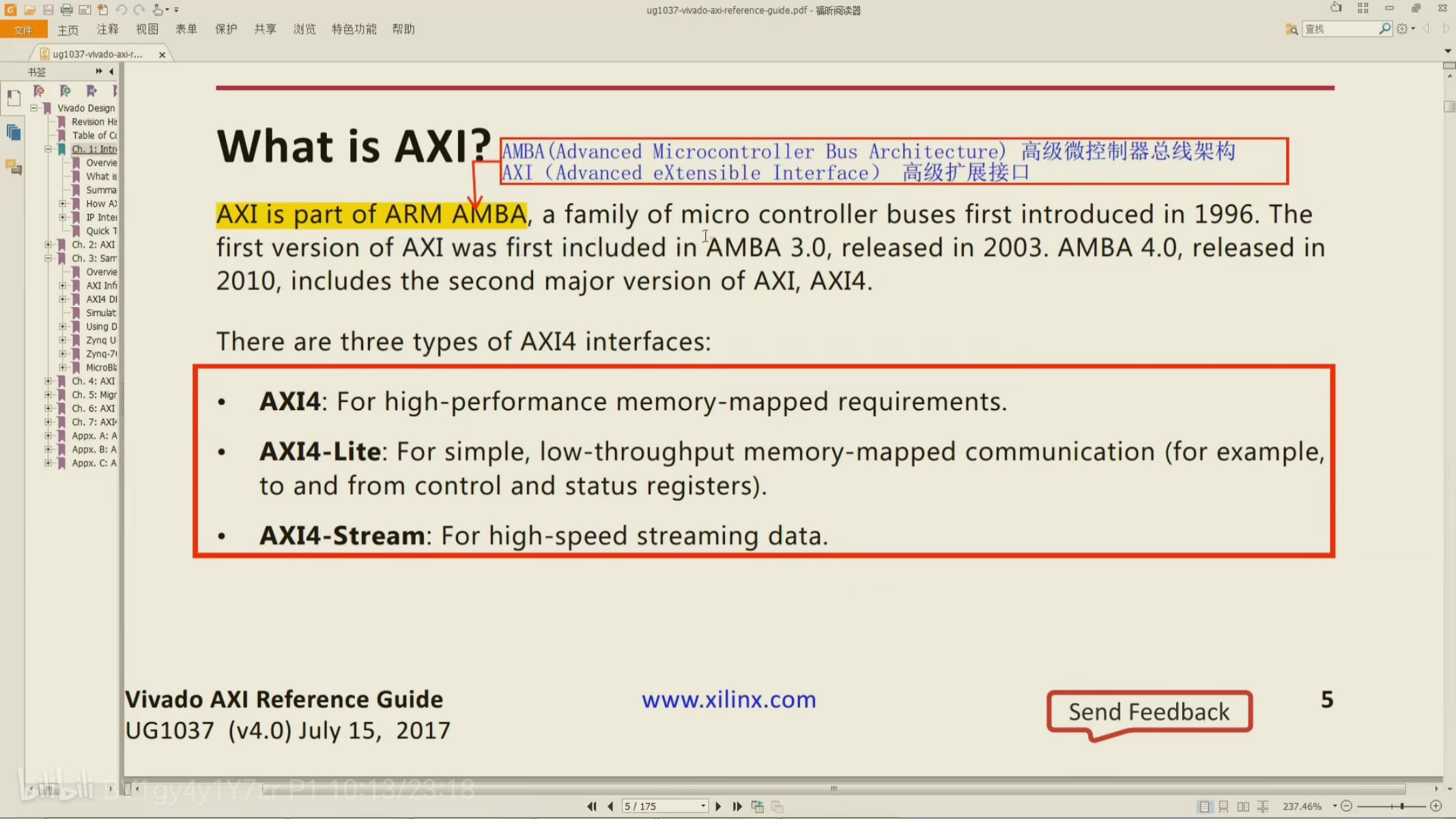

1. 关于AXI4

AXI 是 ARM公司提出的AMBA接口规范中的一种类型

AMBA:Adavanced Microncontroller Bus Architecture

Xilinx 对AXI-4的优势做了一个总结 UG1037

- AXI如何工作?

- 五个独立通道

- 读地址通道

- 读数据通道

- 写地址通道

- 写数据通道

- 写响应通道

- 基于传输通路的Valid和Ready信号握手跳转

- 时序图:pg058-blk-mem0gen.pdf

- 五个独立通道

2.分类

- AXI4 : 由于读写地址通道是分离的,所以支持双向同时传输:突发长度最大为256

- AXI4-Lite : 和AXI4比较类似,但不支持突发传输

- AXI4-Stream:只有一个单一数据通道,和AXI4的写数据通道比较类似,突发长度不受限制

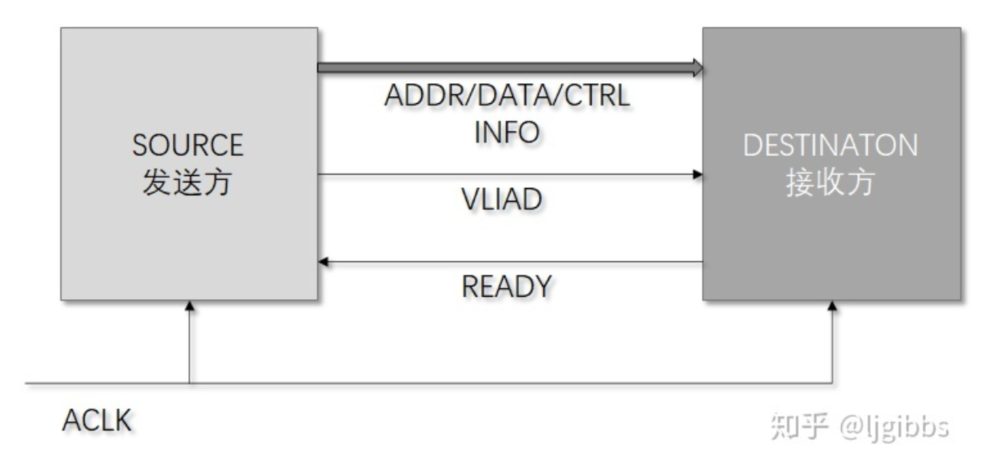

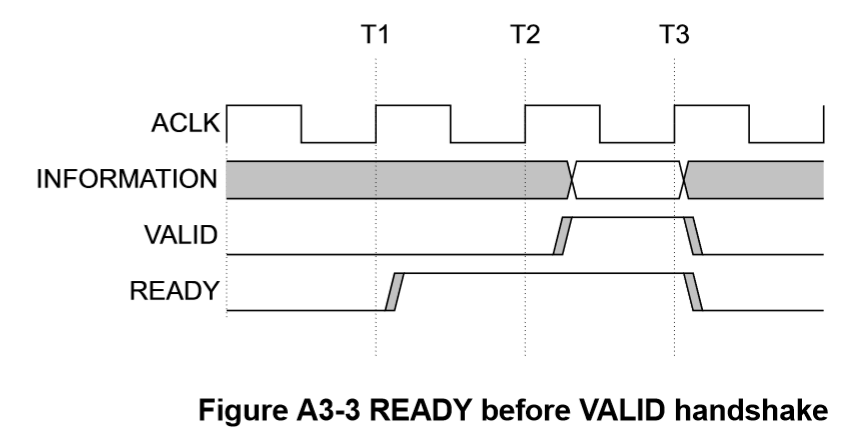

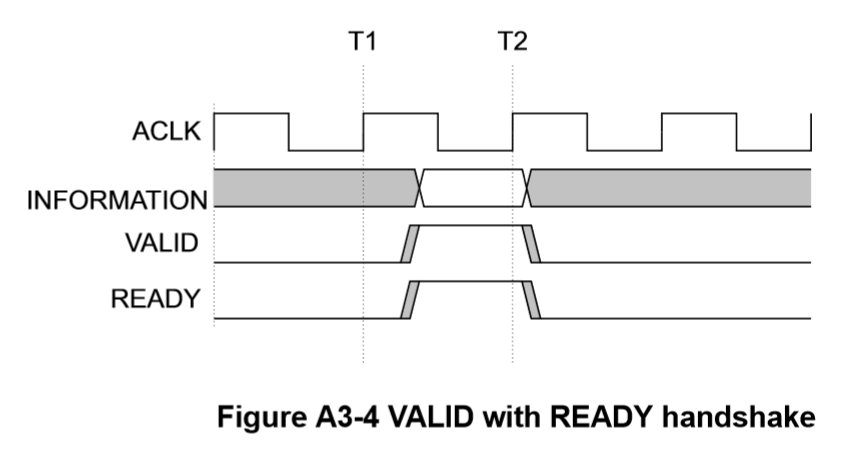

3.VALID/READY 握手机制

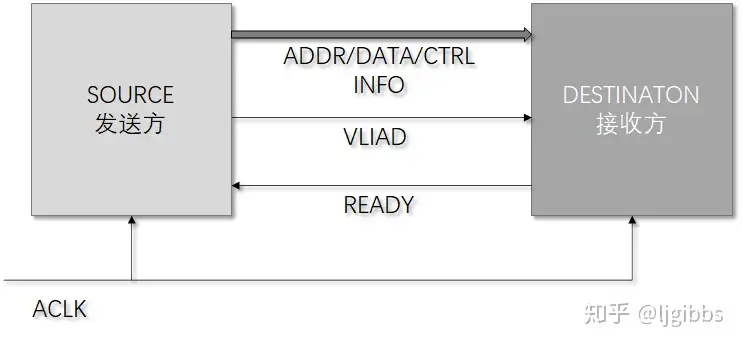

key1: 双向流控

作为一种双向流控机制,VALID/READY 机制可以使发送接收双方都有能力控制传输速率。

在握手机制中,通信双方分别扮演发送方(Source)和接收方(Destination),两者的操作(技能)并不相同

发送方置高 VALID 信号表示发送方已经将数据,地址或者控制信息已经就绪,并保持于消息总线上。

接收方置高 READY 信号表示接收方已经做好接收的准备。

当双方的 VALID/READY 信号同时为高,在时钟 ACLK 上升沿,完成一次数据传输。所有数据传输完毕后,双方同时置低自己的信号。

所谓的双向流控机制,指的是发送方通过置起 VALID 信号控制发送的时机与速度,接收方也可以通过 READY 信号的置起与否控制接收速度。

发送方拥有传输的主动权,但接收方在不具备接收能力时,也能够置低信号停止传输,反压发送方。

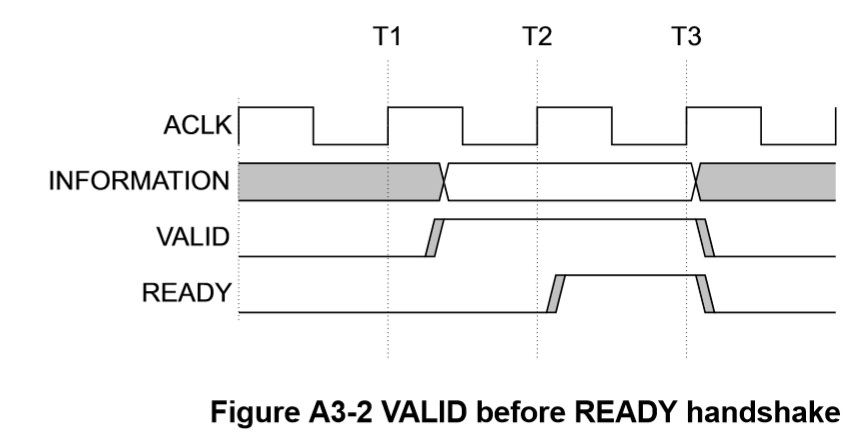

key2: VALID/READY的三种情况

- VALID信号先到达

协议规定在这种情况下,VALID 信号一旦置起就不能置低,直到完成握手(handshake occurs),至少传输一周期数据。

在设计接收方逻辑时,检测到 VALID 信号置起,如果系统正忙,完全可以让发送方等待,发送方在完成传输之前都不会置低 VALID 信号,不需要考虑发送方撤销传输的可能。

A source is not permitted to wait until READY is asserted before asserting VALID.

module axi_src

...

//assign VALID = SRC_CONDITION && READY;//NOT permitted and may cause deadlock

assign VALID = SRC_CONDITION;//permitted

...

endmodule

module axi_dst

...

assign READY = CONDITION && VALID;//permitted

...

endmodule发送方准备发送,置起 VALID 信号是完全主动与独立的过程。接收方 READY 信号按照协议可以依赖发送方 VALID 信号**,但如果此时发送方也依赖接收方信号,就会造成死锁的情况,所以协议在这里强调了 VALID 信号的主动性。**

READY信号先到达

READY 信号很自由,可以等待 VALID 信号到来再做响应,但也完全可以在 VALID 信号到来前就置高,表示接收端已经做好准备了。

READY 信号与 VALID 不同,接收方可以置起 READY 之后发现:其实我好像还挺忙,然后置低 READY 信号。只要此时 VALID 信号没有置起,这种操作是完全可以。

同时到达

同时到达就很简单,等到下一个时钟上升沿 T2,传输就这么轻松愉快地在一个时钟周期里完成了

key3: 深入的细节

协议建议 AW/AR READY 信号(这里 AW/AR 指的是读写地址通道的 READY 信号,将在第二章中正式引入)的默认电平为高电平。若默认电平为低,则每次传输至少需要 2 个周期才能完成,第一个周期置高 VALID 信号,第二个周期从机才会置高 READY 信号。相当于每次传输增加 1 个周期时间开销,这在某些情况下会对传输效率有较大的影响。

4. 五个独立通道

AXI4 总线的一大特征是它有 5 个独立的传输通道,这些通道都只支持单向传输

在 AXI 总线传输中,通道两端分为 Master 主机与 Slave 从机,主机总是发起读写请求的一方。常见的主机有CPU、DMA,

而存储介质控制器(比如 DDR 控制器)则是典型的从机。

主机可能通过从机读取或者写入存储介质。而显然从机不可能主动向 CPU 写入数据。

| 名称 | 英文 | |

|---|---|---|

| 读地址 | read address | 写入本次传输操作所需的地址和控制信息,读写操作都拥有各自的地址通道 |

| 读数据 | read Data | 读数据通道上包括从机发送给主机的读数据,以及从机对于本次读传输操作的回复,具体的读操作状态回复情况会在之后讨论。总线数据位宽可以是 8,16,64,128,256,512 或者是 1024 比特。 |

| 写地址 | write address | 写入本次传输操作所需的地址和控制信息,读写操作都拥有各自的地址通道 |

| 写数据 | write data | 写数据通道用于将主机的写数据传输至从机,位宽和RC的数据位宽相同。WC 有一点 RC 所不具有的特性是拥有 STROBE 信号,用于标识写数据中有效的传输字节。即有些无效的数据,出于减少主机工作量的目的,或者在读写宽度不对称时,被放到写数据通道上和有效数据一起发送。而 STROBE 的信号的作用就是标识出这些无用的数据,告知从机不需要接收无用数据。(Master:我太懒,以至于把所有信号都送过来了) |

| 写回复 | write response | 用于从机将写操作响应回复给主机。所有写传输操作都需要以写回复通道上接收写响应作为完成信号。写回复是针对一次传输操作(transcation)的,而不是针对每一次写数据(data transfer)。 |

PS: 没有读回复 通道:

回复可以合并在读数据通道中,搭个顺风车

但写回复通道的数据流向就和写数据相反。写数据是从主机到从机,而写回复为从机报告写操作的完成情况,流向为从机到主机,无法合并到写数据通道中,另一方面,写回复又是不可或缺的,所以就有了一条独立的写回复通道

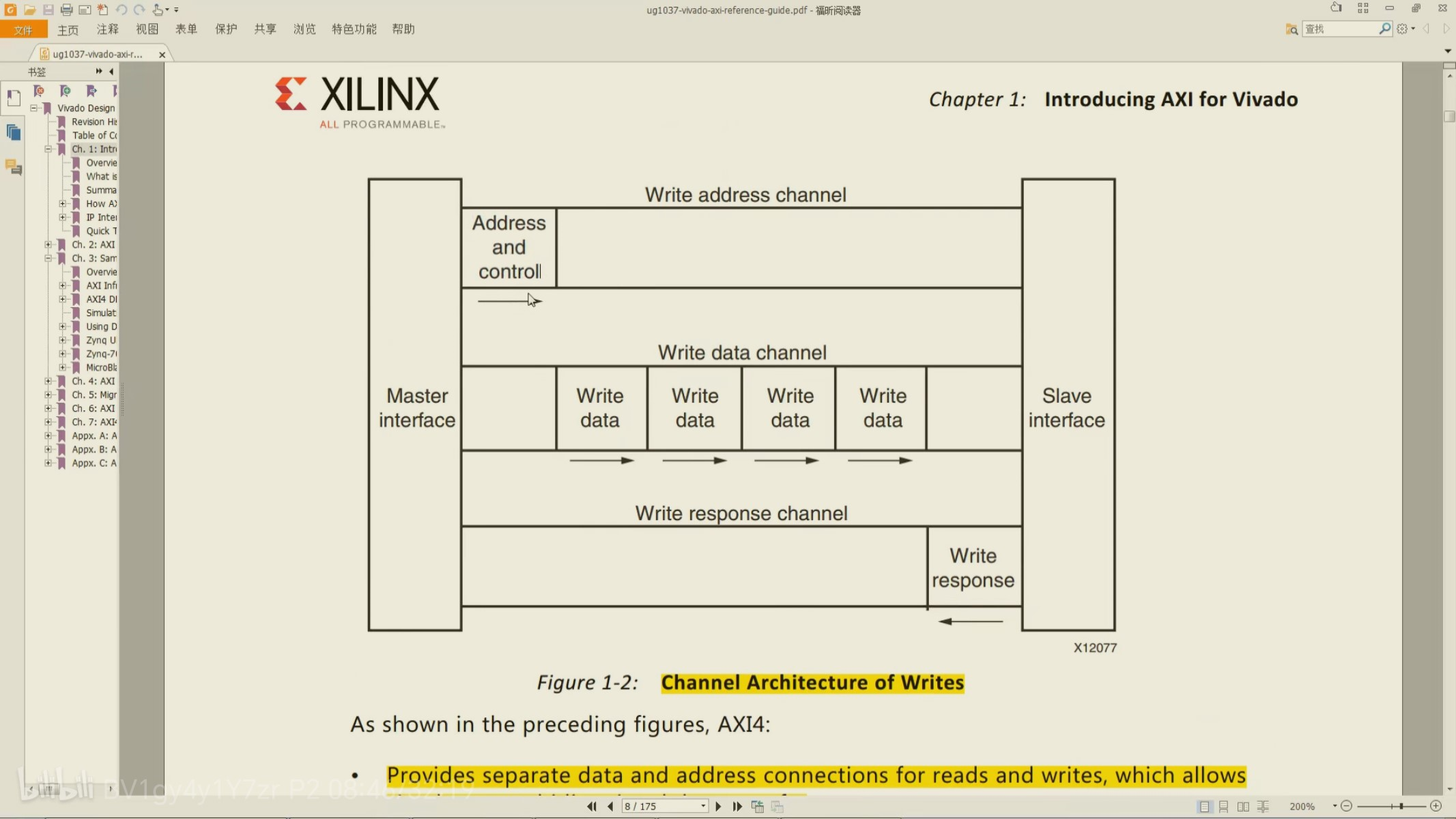

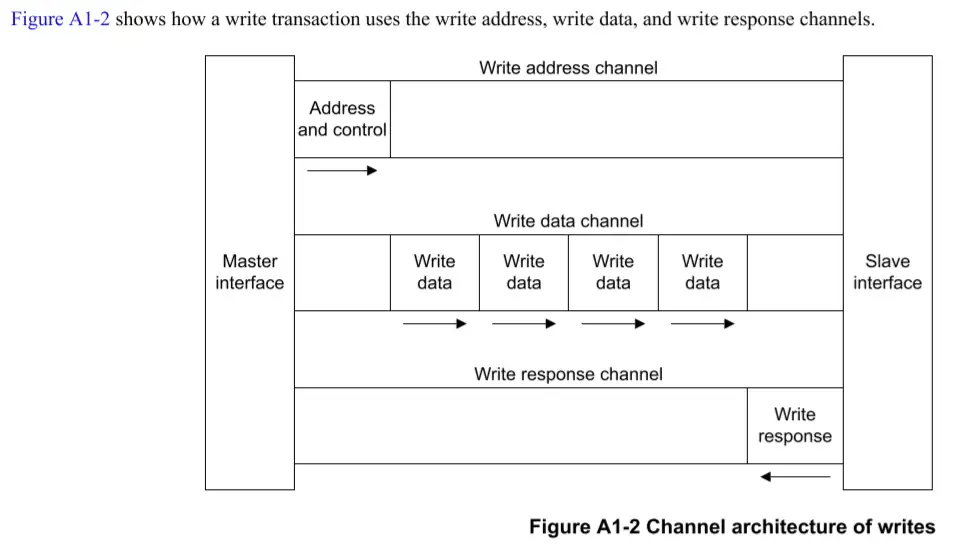

4.1 写传输操作(Write transcation ) 中的通道们

主机首先在写地址通道(AWC)上告知从机本次传输操作(transcaction,对应后文中的"传输操作")的特性,包括地址和控制信息。

然后,在写数据通道(WDC)向从机写入数据,一次传输操作中可能包括多个数据传输(data transfer)。

最后,从机在接收到写数据后,通过写回复通道(RC)将本次传输操作的响应告知主机。主机以收到从机的响应信号,作为本次传输操作结束的标志。手册中强调,写回复是针对整个传输操作(transcaction)的,而不是针对每个写入数据(data transfer)。

所有传输操作中, 写回复和写数据通道必然满足:写回复必然是在收到传输操作中最后一个写数据之后触发

AWC 与 WC 的关系并不局限于一种情况。一般来说,写数据都发生在写地址操作之后,但也不是绝对的,在有些情况下,可以先写数据,或者在同一周期写入数据与地址,都是允许的。这也表现了 AXI 通道之间的独立性。

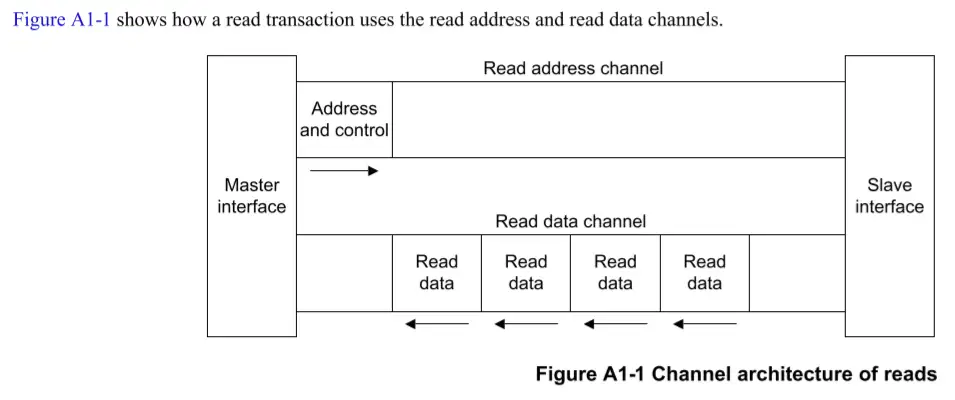

4.2 读操作(Read transcation)中的通道们

读操作只涉及两个通道,首先主机在读地址通道(ARC)上写入本次传输操作(Transcation)待读取数据的地址以及控制信息。

从机在接收到地址后,将该地址上的数据通过读数据通道(RC)传输给主机。

4.3 基于突发传输的AXI总线

简单来说,主机可以写入起始地址以及突发传输的长度等信息,从机将起始地址开始,依次接收主机传输的写数据,或者读取连续地址上的数据,作为读数据传输给主机。

5. 通道上的信号们

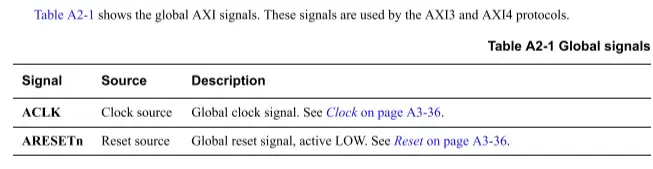

5.1 全局信号(时钟、使能)

注意:AResetn 一般是一个同步复位信号,A 代表 AXI,而不是 Async

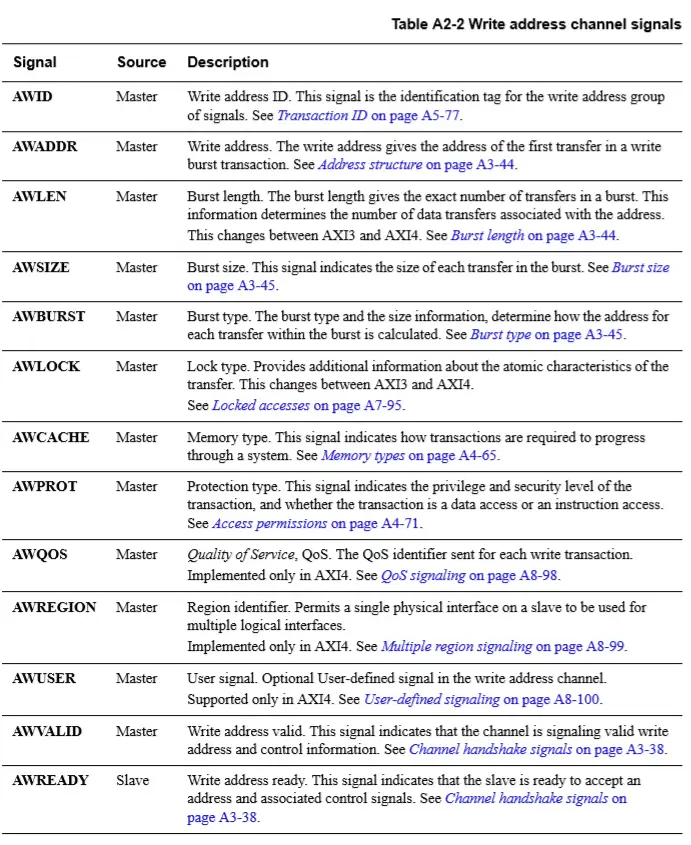

5.2 写地址通道(读地址通道类似)

可分为:经常用到的基础信号、突发传输的控制信号、内存访问相关以及其他的在基础阶段不是很常用的信号

- 基础信号

- AWADDR:传输操作的起始地址

- AWVALID 以及 AWREADY :所有通道都使用的握手信号

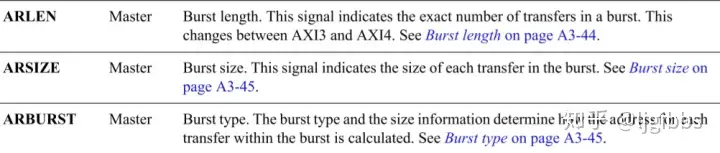

- 突发传输的控制信号 : 传输一次起始地址后,进行多次地址上连续的读写操作

- AWLEN :突发传输的长度,即在一次突发传输中数据传输的个数

- AWSIZE :每次突发传输中的数据传输的位宽

- AWBURST :突发传输的类型

- ......

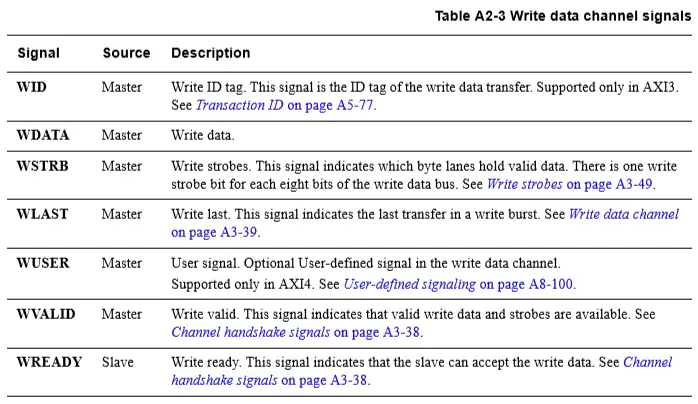

5.3 写数据通道

AXI4 不再支持 WID 信号,这和 AXI4 的乱序机制有关,AXI4 规定所有数据通道的数据必须顺序发送。

WDATA 与常见的握手信号不再赘述,WDATA 的可使用位宽可以见上文。

WSTRB 信号用于标记传输数据中有效的字节,每个 WSTRB 位对应一个字节的位宽,比如数据位宽为 64 位,那么 WSTRB 信号的位宽就是 1 个字节,共 8 位。

WLAST 标识一次突发传输中最后一次数据传输,如果没有正确的 WLAST 的信号,就会造成写入地址的混乱,导致从机无法正确接收写数据,从而造成从机不再拉高 READY 信号的现象。

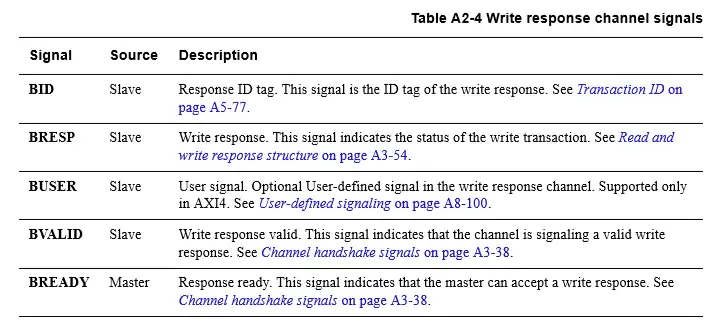

5.4 写回复通道

与写数据通道不同,写回复通道支持 BID,即支持乱序的写回复,关于乱序的问题,我们稍后再谈。BRESP 回复上一次的写状态。

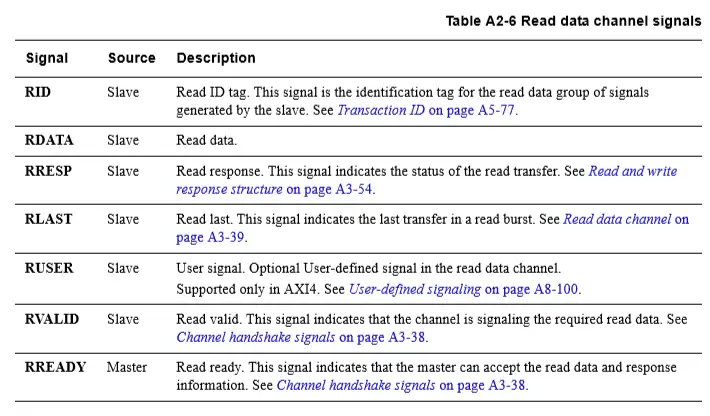

5.5 读数据通道

读数据通道与写数据通道类似,区别有两点:

一,支持 RID 信号。

二,因为读回复信息在读数据通道上传递,所以集成了 RRESP 信号,用于返回读状态,值得注意的是读回复信号和读数据一样,发送方(source)为从机(slave)。

5.6 通道间的关系

一般情况下 AXI 的五个通道之间是独立的。但凡事都免不了例外。AXI 的通道间需要保证以下三种联系(relationship):

- 写回复必须在其所属传输的最后一个写数据完成后(write response must follow the last write transfer in the transaction)

- 读数据必须在接收到读地址信号后产生

- 通道间的握手需要满足通道间的握手依赖性(handshake dependencies)

5.7 握手依赖关系

协议规定握手依赖的目的是为了防止死锁(deadlock)

- 发送方 VALID 一定不能依赖接收方 READY 信号

- 接收方 READY 信号可以检测到 VALID 置起后再置起有效,换句话说,可以依赖 VALID 信号

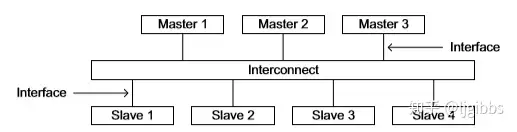

5.8 拓扑链接

- 单对单

单对多:AXI 总线需要借助总线互联IP( Interconnect )来实现多对的的拓扑,结构如下图。Interconnect 拥有多个 Master/Slave 接口,并在内部基于轮询或者优先级策略对多路数据进行路由转发

img AXI 协议并没有对写数据以及写地址通道中的握手信号先后顺序做出规定。因此,实现中数据可以先于地址完成握手。这适用于一些情况,手册中举了个例子,比如写地址通道为了满足时序,触发器的级数与写数据通道不同,这样一来两通道握手的先后顺序可能不同。这反映了 AXI 通道间的独立性,利用该特性可调整路径中的触发器,满足时序约束

6. 传输事务结构

6.1 Burst-based的AXI协议

在 AXI 传输事务(Transaction)中,数据以突发传输(Burst)的形式组织。一次突发传输中可以包含一至多个数据(Transfer)。每个 transfer 因为使用一个周期,又被称为一拍数据(Beat)。

两个 AXI 组件为了传输一组数据而进行的所有交互称为 AXI Transaction,AXI 传输事务,包括所有 5 个通道上的交互。

不严谨地说

AXI Transaction =MAXI Burst ,M >= 1 AXI Burst = N *** AXI Transfer(AXI beat)* ,N >= 1

6.2 传输事务结构(Transaction structure)

在整个传输事务过程中,主机首先将接下来 burst 传输的控制信息以及数据首个字节的地址传输给从机,这个地址被称为起始地址。在本次 burst 后续传输期间,从机将根据控制信息计算后续数据的地址。

控制信息以及起始地址在读/写地址通道(AWC/ARC)传输

注意:单次 burst 传输中的数据,其地址不能跨越 4KB 边界。

地址通道中传输的控制信息中包括三项突发传输相关的信号(AR/AW 均一致,下图为以 AR 为例):

突发传输长度 burst length : 指一次突发传输中包含的数据传输(transfer)数量,在协议中使用 AxLen 信号控制

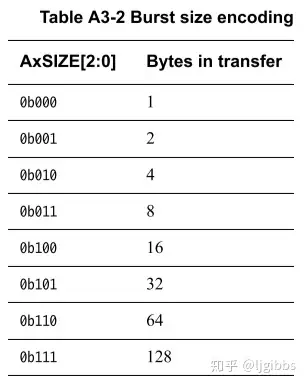

突发传输宽度 burst size : 指传输中的数据位宽,具体地是每周期传输数据的字节数量,在协议中使用 AXSIZE 信号控制

传输宽度 = 2 ^ AXSIZE

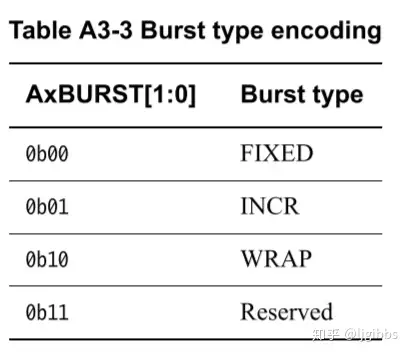

突发传输类型(AxBURST):类型共有三种,分别为 FIXED,INCR 以及 WRAP,使用 2 位二进制表示。

img FIXED 类型中, burst 中所有数据都使用起始地址。该模式适合对某个固定地址进行多次数据更新,比如读写一个 fifo 时,读写地址就是固定的。

INCR 类型 最为常用,后续数据的地址在初始地址的基础上进行递增,递增幅度与传输宽度相同。适合对于 RAM 等通过地址映射(mapped memory)的存储介质进行读写操作。

WRAP 类型 比较特殊,首先根据起始地址得到绕回边界地址(wrap boundary)与最高地址。当前地址小于最高地址时,WRAP 与 INCR 类型完全相同,地址递增。但到递增后的地址到达最高地址后,地址直接回到绕回边界地址,再进行递增,就这样循环往复。最高地址由绕回边界地址计算得到:wrap boundary + (N_bytes x burst_len)

7. 其他